Lo svantaggio principale di circuito combinatorio ovvero, non utilizza alcuna memoria per salvare lo stato presente e precedente. Quindi il precedente stato di ingresso non ha alcun effetto sullo stato attuale del circuito. Considerando che, il circuito sequenziale ha memoria, quindi l'output può variare in base all'input. Questo tipo di circuiti utilizza input, output, clock e un elemento di memoria precedenti. Qui gli elementi di memoria possono essere latch o flip-flop. I circuiti sequenziali sono progettati con vari metodi come l'utilizzo di ROM e flip, PLA, CPLD (Complex Programmable Logic Device) , FPGA (Field Programmable Gate Array) . In questo articolo, discuteremo solo su come progettare un circuito sequenziale utilizzando gli PLA.

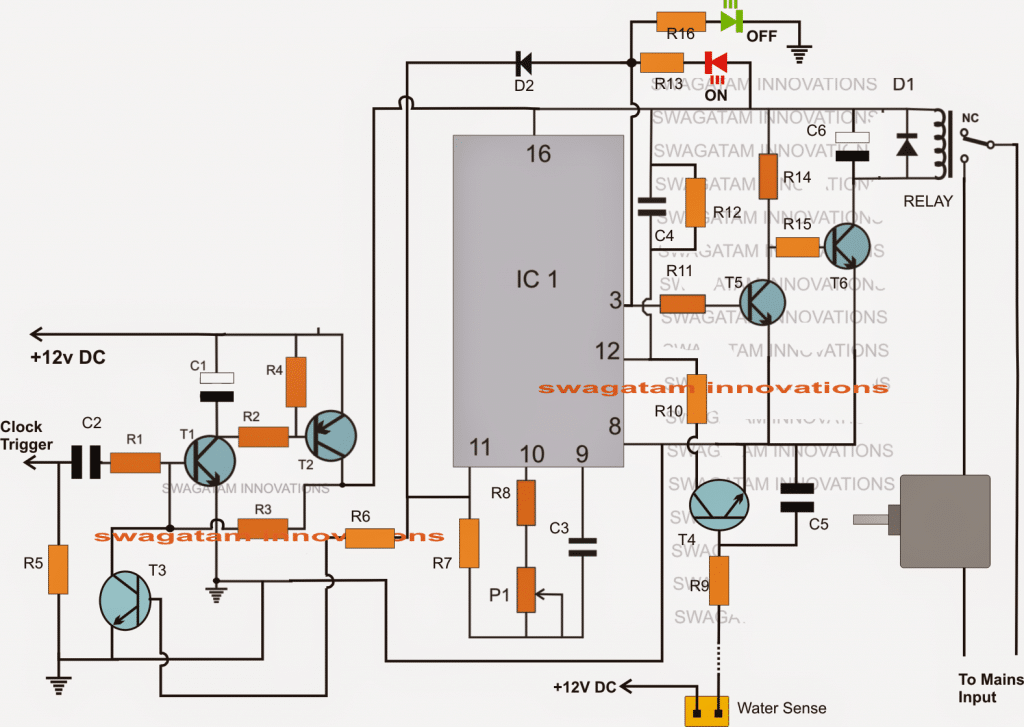

Lo schema a blocchi del circuito sequenziale come mostrato di seguito:

Schema a blocchi del circuito sequenziale

Progettazione di circuiti sequenziali utilizzando PLA

Circuiti sequenziali può essere realizzato utilizzando PLA (Programmable Logic Arrays) e flip-flop. In questo progetto, l'assegnazione di stato può essere importante perché l'uso di un'assegnazione di stato buono può ridurre il numero richiesto di termini di prodotto e, quindi, ridurre la dimensione richiesta del PLA. Un termine prodotto definito come la congiunzione di letterali, dove ogni letterale è una variabile o la sua negazione.

Consideriamo il progetto un convertitore di codice. La tabella di stato mostrata di seguito nella tabella può essere realizzata utilizzando un PLA e tre infradito come mostrato nella figura sottostante. Questa configurazione circuitale è molto simile al design basato su ROM flip-flop, tranne per il fatto che la ROM è sostituita dal PLA di dimensioni adeguate. L'assegnazione di stato porta alla tabella di verità fornita di seguito. Questa tabella potrebbe essere memorizzata in un PLA con quattro ingressi, 13 termini di prodotto e quattro uscite, ma ciò offrirebbe dimensioni leggermente ridotte rispetto alla ROM a 16 parole.

| X Q1 Q2 Q3 | Con D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tabella: tabella della verità

PRESENTE STATO

| PROSSIMO STATO X = 0 1 | PRESENTE USCITA (Z) |

| PER | AVANTI CRISTO | 1 0 |

B C | D E E E | 1 0 0 1 |

D E | H H H M | 0 1 1 0 |

H M | AA PER - | 0 1 1 - |

Tabella: tabella di stato

Progettazione di circuiti sequenziali utilizzando PLA

Input Output Equazioni derivate da Karnaugh Map

In questo caso, poiché ci sono sette stati, sono necessari tre flip-flop D. Pertanto, è richiesto un circuito PLA con 4 ingressi e 4 uscite. Se si considera l'assegnazione dello stato del convertitore di codice, l'equazione di output risultante e le equazioni di input del flip-flop D derivate dal Karnaugh possono essere scritte le seguenti equazioni

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | Con D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1-0 1 0 0 - 0 - - 0 undici

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

La tabella PLA che corrisponde a queste equazioni è riportata nella tabella sopra. Questa tabella può essere realizzata utilizzando PLA con quattro input, sette termini di prodotto e quattro output. Per verificare inizialmente il funzionamento del progetto di cui sopra, supponiamo che X = 0 e Q1Q2Q3 = 000. Questo seleziona le righe - - 0- e 0 - - -0 nella tabella, quindi Z = 0 e D1D2D3 = 100. Dopo il fronte di clock attivo, Q1Q2Q3 = 100. Se l'input successivo è X = 1, vengono selezionate le righe - - 0 - e - 1- -, quindi Z = 0 e D1D2D3 = 110. Dopo il fronte di clock attivo, Q1Q2Q3 = 110.

Array logico programmabile (PLA)

L'array logico programmabile è un dispositivo logico programmabile. Viene generalmente utilizzato per implementare circuiti logici combinatori. Il PLA ha un set di piani AND programmabili (AND array), che si collegano a un set di piani OR programmabili (OR array), che possono quindi essere provvisoriamente integrati per produrre un output. Questo layout consente di sintetizzare un gran numero di funzioni logiche in somma dei prodotti (SOP) forme canoniche. Di seguito viene fornito un semplice diagramma a blocchi di un PLA.

Schema a blocchi di un PLA

La principale differenza tra PLA e PAL (logica array programmabile) è,

PLA: Entrambi Piano AND e piano OR sono programmabili.

PAL: solo il piano AND è programmabile, mentre il piano OR è fisso.

Per una migliore comprensione del PLA, qui stiamo considerando l'esempio seguente.

Proviamo a implementare queste funzioni f1 e f2 sono dati come

Gli ingressi x1, x2, x3 ei loro rispettivi segnali complementati sono dati al piano AND programmabile, lì avremo uscite del piano AND come minterm P1, P2, P3. Quindi questi segnali vengono inviati al piano OR programmabile per produrre la funzione di uscita richiesta f1 e f2 (somma dei prodotti). La figura seguente descrive l'implementazione a livello di gate del PLA per una determinata funzionalità.

Attuazione del PLA

Questo è tutto sulla progettazione di circuiti sequenziali utilizzando PLA. Riteniamo che le informazioni fornite in questo articolo siano utili per una migliore comprensione di questo concetto. Inoltre, qualsiasi domanda riguardante questo articolo o qualsiasi aiuto in realizzazione di progetti elettrici ed elettronici , puoi avvicinarci commentando nella sezione commenti qui sotto. Ecco una domanda per te, Cosa si intende per circuito sequenziale?