Diversi tipi di sistemi digitali sono costruiti da pochissimi tipi di configurazioni di rete di base come porta AND, porta NAND, porta Or, ecc ... Questi circuiti elementari vengono utilizzati più e più volte in varie combinazioni topologiche. Oltre a eseguire la logica, i sistemi digitali devono memorizzare anche numeri binari. Per queste celle di memoria, note anche come CIABATTE INFRADITO' sono progettati. Per eseguire alcune funzioni come l'addizione binaria. Quindi, per eseguire tali funzioni, combinazioni di porte logiche e FLIP-FLOP sono progettati su un CI a chip singolo. Questi circuiti integrati costituiscono gli elementi costitutivi pratici dei sistemi digitali. Uno di questi elementi costitutivi utilizzati per l'aggiunta binaria è il Carry Look-ahead Adder.

Che cos'è un Carry Look-ahead Adder?

Un computer digitale deve contenere circuiti in grado di eseguire operazioni aritmetiche come addizione, sottrazione, moltiplicazione e divisione. Tra queste, l'addizione e la sottrazione sono le operazioni di base mentre la moltiplicazione e la divisione sono rispettivamente l'addizione e la sottrazione ripetute.

Per eseguire queste operazioni, i 'circuiti sommatori' vengono implementati utilizzando porte logiche di base. Circuiti sommatori si sono evoluti come Half-adder, Full-adder, Ripple-carry Adder e Carry Look-ahead Adder.

Tra questi Carry Look-ahead Adder è il circuito sommatore più veloce. Riduce il ritardo di propagazione, che si verifica durante l'aggiunta, utilizzando circuiti hardware più complessi. È progettato trasformando il circuito Ripple-carry Adder in modo tale che la logica di carry del sommatore venga modificata in una logica a due livelli.

4 bit Carry Look-ahead Adder

In sommatori paralleli, l'output di riporto di ciascun sommatore completo viene fornito come input di riporto allo stato di ordine superiore successivo. Quindi, questi sommatori non è possibile produrre riporto e sommare uscite di alcuno stato a meno che un ingresso riporto non sia disponibile per quello stato.

Quindi, affinché avvenga il calcolo, il circuito deve attendere fino a quando il bit di riporto si propaga a tutti gli stati. Ciò induce il ritardo di propagazione del trasporto nel circuito.

Sommatore da trasporto a 4 bit

Considera il circuito sommatore ripple a 4 bit sopra. Qui la somma S3 può essere prodotta non appena vengono forniti gli ingressi A3 e B3. Ma il riporto C3 non può essere calcolato finché non viene applicato il bit di riporto C2 mentre C2 dipende da C1. Pertanto, per produrre risultati finali di stato stazionario, il carry deve propagarsi attraverso tutti gli stati. Ciò aumenta il ritardo di propagazione del riporto del circuito.

Il ritardo di propagazione del sommatore è calcolato come “il ritardo di propagazione di ogni porta moltiplicato per il numero di stadi del circuito”. Per il calcolo di un gran numero di bit, è necessario aggiungere più stadi, il che peggiora notevolmente il ritardo. Quindi, per risolvere questa situazione, è stato introdotto Carry Look-ahead Adder.

Per comprendere il funzionamento di un Carry Look-ahead Adder, di seguito viene descritto un Carry Look-ahead Adder a 4 bit.

Diagramma logico sommatore a 4 bit

In questo sommatore, l'ingresso di riporto in qualsiasi fase del sommatore è indipendente dai bit di riporto generati negli stadi indipendenti. Qui l'uscita di qualsiasi stadio dipende solo dai bit aggiunti nelle fasi precedenti e dall'ingresso di riporto fornito nella fase iniziale. Quindi, il circuito in qualsiasi fase non deve attendere la generazione del bit di riporto dallo stadio precedente e il bit di riporto può essere valutato in qualsiasi istante di tempo.

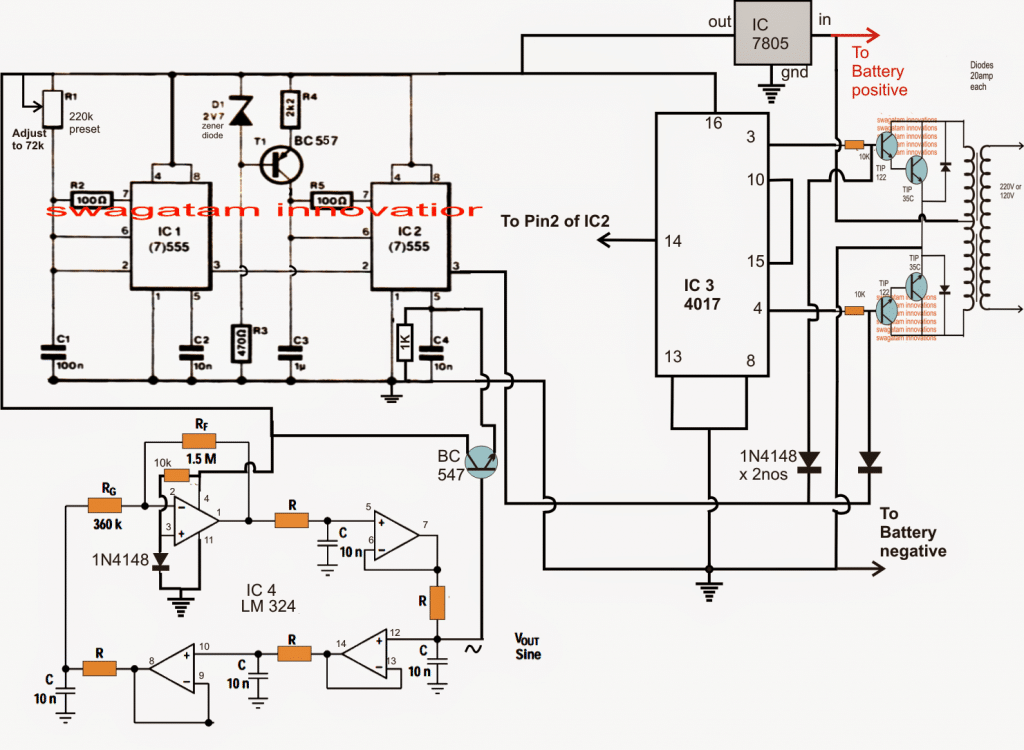

Tabella della verità di Carry Look-ahead Adder

Per derivare la tabella di verità di questo sommatore, vengono introdotti due nuovi termini: Carry generate e carry propagate. Carry genera Gi = 1 ogni volta che viene generato un carry Ci + 1. Dipende dagli ingressi Ai e Bi. Gi è 1 quando sia Ai che Bi sono 1. Quindi, Gi è calcolato come Gi = Ai. Bi.

Il carry propagato Pi è associato alla propagazione del carry da Ci a Ci + 1. È calcolato come Pi = Ai ⊕ Bi. La tabella di verità di questo sommatore può essere derivata dalla modifica della tabella di verità di un sommatore completo.

Usando i termini Gi e Pi, Sum Si e Carry Ci + 1 sono indicati come di seguito:

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Pertanto, i bit di riporto C1, C2, C3 e C4 possono essere calcolati come

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Si può osservare dalle equazioni che portano Ci + 1 dipende solo dal riporto C0, non dai bit di riporto intermedi.

Carry-Look-ahead-Adder-Truth-Table

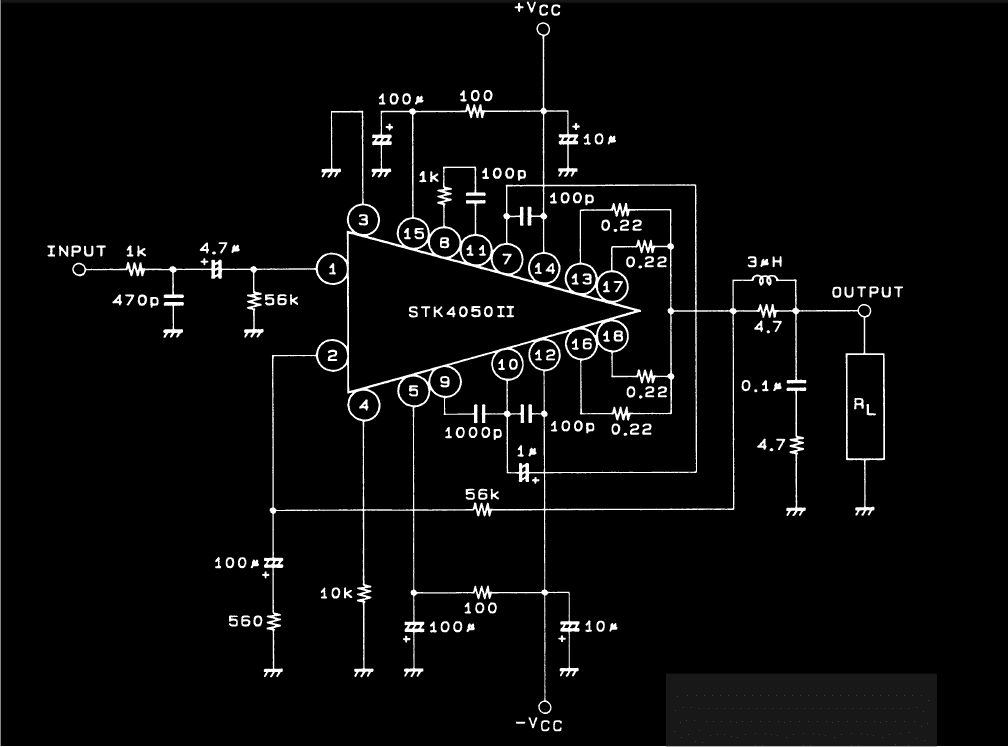

Schema elettrico

Le equazioni di cui sopra sono implementate utilizzando circuiti combinatori a due livelli insieme a porte AND, OR, dove si presume che le porte abbiano più ingressi.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

Di seguito viene fornito il circuito Carry Look-ahead Adder da 4 bit.

Schema del circuito sommatore a 4 bit

I circuiti Carry Look-ahead Adder a 8 bit e 16 bit possono essere progettati collegando a cascata il circuito sommatore a 4 bit con la logica di riporto.

Vantaggi di Carry Look-ahead Adder

In questo sommatore, il ritardo di propagazione è ridotto. L'uscita di riporto in qualsiasi fase dipende solo dal bit di riporto iniziale della fase iniziale. Utilizzando questo sommatore è possibile calcolare i risultati intermedi. Questo sommatore è il sommatore più veloce utilizzato per il calcolo.

Applicazioni

I Carry Look-ahead Adders ad alta velocità vengono utilizzati come implementati come IC. Quindi, è facile incorporare il sommatore nei circuiti. Combinando due o più sommatori, i calcoli di funzioni booleane di bit più alti possono essere eseguiti facilmente. Anche qui l'aumento del numero di gate è moderato se utilizzato per bit più alti.

Per questo Adder c'è un compromesso tra area e velocità. Quando viene utilizzato per calcoli di bit più elevati, fornisce un'elevata velocità ma aumenta anche la complessità del circuito, aumentando così l'area occupata dal circuito. Questo sommatore viene solitamente implementato come moduli a 4 bit che vengono messi in cascata insieme quando vengono utilizzati per calcoli superiori. Questo sommatore è più costoso rispetto ad altri sommatori.

Per il calcolo booleano nei computer, vengono utilizzati regolarmente sommatori. Charles Babbage ha implementato un meccanismo per anticipare il carry bit nei computer, per ridurre il ritardo causato dal ripple carry adders . Durante la progettazione di un sistema, la velocità di calcolo è il fattore decisivo più alto per un progettista. Nel 1957, Gerald B. Rosenberger brevettò il moderno Binary Carry Look-ahead Adder. Sulla base dell'analisi del ritardo di gate e della simulazione, sono in corso esperimenti per modificare il circuito di questo sommatore per renderlo ancora più veloce. Per un addizionatore look-ahead carry n-bit, qual è il ritardo di propagazione, quando un ritardo di ogni gate è 20?

Credito d'immagine