Il transistor MOS è l'elemento fondamentale nella progettazione di circuiti integrati su larga scala. Questi transistor sono generalmente classificati in due tipi PMOS e NMOS. La combinazione di transistor NMOS e PMOS è nota come a Transistor CMOS . Il diverso porte logiche e altri dispositivi logici digitali implementati devono avere logica PMOS. Questa tecnologia è poco costosa e ha una buona resistenza alle interferenze. Questo articolo discute uno dei tipi di transistor MOS come un transistor PMOS.

Cos'è il transistor PMOS?

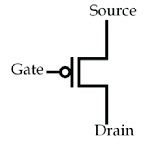

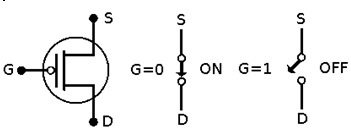

Il transistor PMOS o semiconduttore di ossido di metallo a canale P è un tipo di transistor in cui i droganti di tipo p sono utilizzati nel canale o nella regione di gate. Questo transistor è esattamente l'inverso del transistor NMOS. Questi transistor hanno tre terminali principali; la sorgente, il gate e il drain in cui la sorgente del transistor è progettata con un substrato di tipo p e il terminale di drain è progettato con un substrato di tipo n. In questo transistor, i portatori di carica come i fori sono responsabili della conduzione della corrente. I simboli del transistor PMOS sono mostrati di seguito.

Come funziona il transistor PMOS?

Il funzionamento del transistor di tipo p è del tutto opposto al transistor di tipo n. Questo transistor formerà un circuito aperto ogni volta che riceve una tensione non trascurabile, il che significa che non c'è flusso di elettricità dal terminale gate (G) alla sorgente (S). Allo stesso modo, questo transistor forma un circuito chiuso quando riceve una tensione di circa 0 volt, il che significa che la corrente scorre dal terminale di gate (G) al drain (D).

Questa bolla è anche nota come bolla di inversione. Quindi la funzione principale di questo cerchio è quella di invertire il valore della tensione di ingresso. Se il terminale di gate fornisce una tensione 1, questo inverter la cambierà in zero e funzionerà di conseguenza il circuito. Quindi la funzione del transistor PMOS e del transistor NMOS è completamente opposta. Una volta che li uniamo in un singolo circuito MOS, diventerà un circuito CMOS (complementary metal-oxide semiconductor).

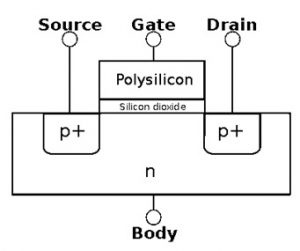

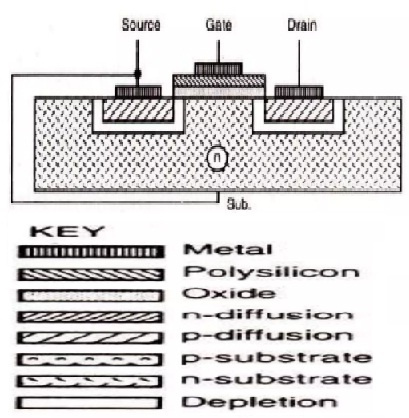

Sezione trasversale del transistor PMOS

Di seguito è mostrata la sezione trasversale del transistor PMOS. Un transistor pMOS è costruito con un corpo di tipo n comprendente due regioni semiconduttrici di tipo p che sono adiacenti al gate. Questo transistor ha un gate di controllo come mostrato nel diagramma che controlla il flusso di elettroni tra i due terminali come source e drain. Nel transistor pMOS, il corpo è tenuto a tensione +ve. Una volta che il terminale di gate è positivo, i terminali di source e drain sono polarizzati inversamente. Una volta che ciò accade, non c'è flusso di corrente, quindi il transistor verrà spento.

Una volta abbassata la tensione di alimentazione al terminale di gate, i portatori di carica positivi saranno attratti nella parte inferiore dell'interfaccia Si-SiO2. Ogni volta che la tensione si abbassa sufficientemente, il canale verrà invertito e creerà un percorso conduttivo dal terminale sorgente allo scarico consentendo il flusso di corrente.

Ogni volta che questi transistor si occupano della logica digitale, di solito hanno due valori diversi solo come 1 e 0 (ON e OFF). La tensione positiva del transistor è nota come VDD che rappresenta il valore logico alto (1) all'interno dei circuiti digitali. I livelli di tensione VDD in Logica TTL erano generalmente intorno ai 5V. Al momento i transistor non possono effettivamente sopportare tensioni così elevate perché in genere vanno da 1,5 V a 3,3 V. La bassa tensione è spesso nota come GND o VSS. Quindi, VSS indica lo '0' logico ed è anche impostato normalmente su 0V.

Circuito a transistor PMOS

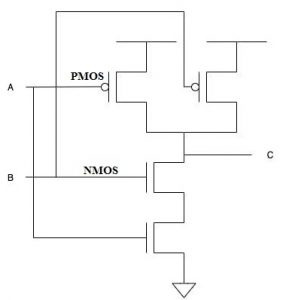

Di seguito è mostrato il design della porta NAND che utilizza il transistor PMOS e il transistor NMOS. Generalmente, una porta NAND nell'elettronica digitale è una porta logica chiamata anche porta NOT-AND. L'uscita di questa porta è bassa (0) solo se i due ingressi sono alti (1) e la sua uscita è complementare a una porta AND. Se uno qualsiasi dei due input è BASSO (0), fornisce risultati di output elevati.

Nel circuito logico sottostante, se l'ingresso A è 0 e B è 0, allora un ingresso di pMOS produrrà '1' e un ingresso di nMOS produrrà '0'. Quindi, questa porta logica genera un '1' logico perché è collegata alla sorgente da un circuito chiuso e staccata da GND attraverso un circuito aperto.

Quando A è '0' e B' è '1', allora un ingresso di pMOS genererà un '1' e un ingresso di NMOS genererà uno '0'. Pertanto, questa porta ne produrrà una logica perché è collegata alla sorgente attraverso un circuito chiuso e staccata da GND da un circuito aperto. Quando A è '1' e B è '0', l'ingresso 'B' di pMOS genererà un'uscita alta (1) e l'ingresso 'B' di NMOS genererà un'uscita bassa (0). Quindi, questa porta logica genererà un 1 logico perché è collegata alla sorgente attraverso un circuito chiuso e staccata da GND da un circuito aperto.

Quando A è '1' e B è '1', allora un ingresso di 'pMOS produrrà uno zero, e un ingresso di nMOS genererà '1'. Di conseguenza, dovremmo verificare anche l'ingresso B di pMOS e nMOS. L'ingresso B di pMOS genererà uno '0' e l'ingresso B di nMOS genererà un '1'. Quindi, questa porta logica genererà uno '0' logico perché è staccata dalla sorgente da un circuito aperto ed è collegata a GND attraverso un circuito chiuso.

Tavola della verità

Di seguito è riportata la tabella di verità del circuito logico di cui sopra.

|

UN |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

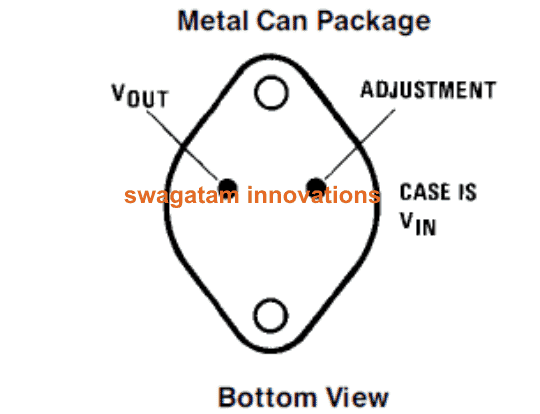

La tensione di soglia del transistor PMOS è normalmente il 'Vgs' necessario per creare il canale noto come inversione di canale. In un transistor PMOS, il substrato e i terminali della sorgente sono semplicemente collegati a 'Vdd'. Se iniziamo a ridurre la tensione facendo riferimento al terminale della sorgente al terminale di gate da Vdd a un punto in cui si nota l'inversione del canale, in questa posizione se si analizza Vgs e la sorgente è all'alto potenziale, si otterrà un valore negativo. Quindi, il transistor PMOS ha un valore Vth negativo.

Processo di fabbricazione PMOS

I passaggi coinvolti nella fabbricazione di transistor PMOS sono discussi di seguito.

Passo 1:

Un sottile strato di wafer di silicio viene trasformato in materiale di tipo N semplicemente drogando materiale fosforoso.

Passo 2:

Uno spesso strato di biossido di silicio (Sio2) viene coltivato su un substrato di tipo p completo.

Passaggio 3:

Ora la superficie è rivestita con un fotoresist sullo spesso strato di biossido di silicio.

Passaggio 4:

Successivamente, questo strato viene semplicemente esposto alla luce UV attraverso una maschera che definisce le regioni in cui deve avvenire la diffusione insieme ai canali del transistor.

Passaggio 5:

Queste regioni vengono attaccate via reciprocamente con il biossido di silicio sottostante in modo che la superficie della fetta sia esposta all'interno della finestra definita dalla maschera.

Passaggio 6:

Il restante fotoresist viene staccato e il sottile strato di Sio2 viene fatto crescere tipicamente di 0,1 micrometri sull'intera superficie del chip. Successivamente, il polisilicio viene posizionato sopra questo per formare la struttura del gate. Un fotoresist viene posizionato sull'intero strato di polisilicio ed espone la luce UV attraverso la maschera2.

Passaggio 7:

Le diffusioni si ottengono attraverso il riscaldamento del wafer alla massima temperatura e il passaggio di gas con le impurità di tipo p desiderate come il boro.

Passaggio 8:

Viene coltivato un biossido di silicio dello spessore di 1 micrometro e su di esso viene depositato del materiale fotoresist. Esporre la luce ultravioletta con mask3 sulle aree preferite di gate, source e drain che vengono incise per eseguire i tagli di contatto.

Passaggio 9:

Ora un metallo o alluminio viene depositato sulla sua superficie dello spessore di 1 micrometro. Anche in questo caso un materiale fotoresist viene fatto crescere su tutto il metallo ed espone la luce UV attraverso la maschera4 che viene incisa per formare il progetto di interconnessione richiesto. La struttura PMOS finale è mostrata di seguito.

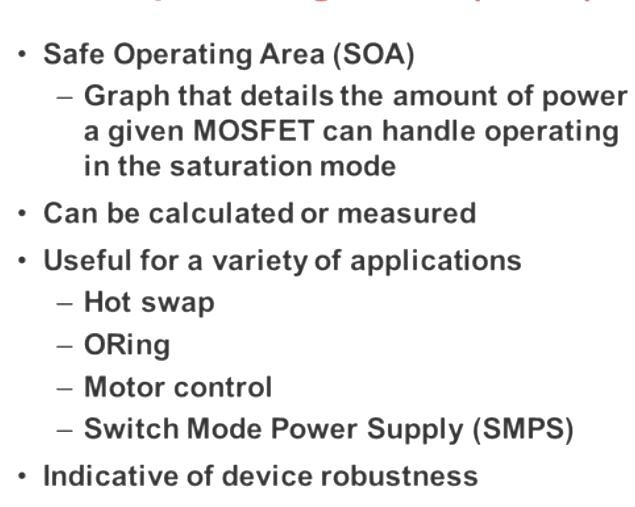

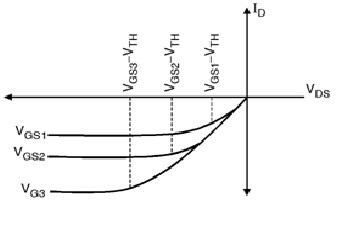

Caratteristiche dei transistor PMOS

Di seguito sono riportate le caratteristiche del transistor PMOS I-V. Queste caratteristiche sono divise in due regioni per ottenere la relazione tra la corrente drain-source (IDS) e le sue tensioni terminali come le regioni lineari e di saturazione.

In una regione di linea, l'IDS aumenterà linearmente quando il VDS (drain to source voltage) viene aumentato mentre nella regione di saturazione, l'IDS è stabile ed è indipendente dal VDS. La relazione principale tra l'ISD (source to drain current) e le sue tensioni terminali è derivata da una procedura simile del transistor NMOS. In questo caso, l'unico cambiamento sarà che i portatori di carica presenti all'interno dello strato di inversione saranno semplicemente buchi. Quando i fori si spostano dalla sorgente al drenaggio, anche il flusso di corrente è lo stesso.

Pertanto, il segno negativo appare all'interno dell'equazione corrente. Inoltre, tutte le polarizzazioni applicate ai terminali del dispositivo sono negative. Quindi, l'ID del transistor PMOS - le caratteristiche VDS sono mostrate di seguito.

L'equazione della corrente di drain per il transistor PMOS nella regione lineare è data come:

ID = – mp Cox

Allo stesso modo, l'equazione della corrente di Drain per il transistor PMOS nella regione di saturazione è data come:

ID = – mp Cox (VSG – | V TH |p )^2

Dove ‘mp’ è la mobilità del foro & ‘|VTH| p' è la tensione di soglia del transistor PMOS.

Nell'equazione precedente, il segno negativo indicherà che l'ID( corrente di scarico ) scorre dallo scarico (D) alla sorgente (S) mentre i fori scorrono nella direzione opposta. Quando la mobilità del foro è bassa rispetto alla mobilità dell'elettrone, i transistor PMOS risentono della capacità del pilotaggio a bassa corrente.

Quindi, si tratta di una panoramica del transistor PMOS o del transistor mos di tipo p: fabbricazione, circuito e funzionamento. PMOS i transistor sono progettati con una sorgente p, un substrato n e un drenaggio. I portatori di carica di PMOS sono buchi. Questo transistor conduce una volta applicata la bassa tensione al terminale di gate. I dispositivi basati su PMOS sono meno soggetti a interferenze rispetto ai dispositivi NMOS. Questi transistor possono essere utilizzati come resistori controllati in tensione, carichi attivi, specchi di corrente, amplificatori a transimpedenza e utilizzati anche in interruttori e amplificatori di tensione. Ecco una domanda per te, cos'è un transistor NMOS?