Il circuito di aggancio fase è uno dei blocchi di base nei moderni sistemi elettronici. Viene generalmente utilizzato in ambito multimediale, comunicazione e in molte altre applicazioni. Esistono due diversi tipi di PLL: lineare e non lineare. Il non lineare è difficile e complicato da progettare nel mondo reale, ma la teoria del controllo lineare è ben modellata nei PLL analogici. Il PLL ha dimostrato che un modello lineare è sufficiente per la maggior parte delle applicazioni elettroniche.

Cos'è un loop ad aggancio di fase?

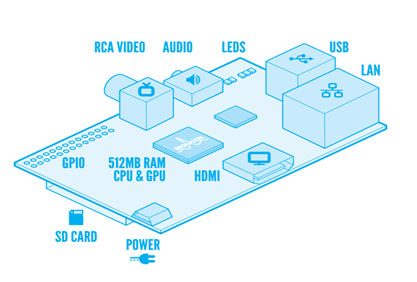

Un anello ad aggancio di fase è costituito da un rilevatore di fase e da un oscillatore controllato in tensione. L'uscita del rilevatore di fase è l'ingresso dell'oscillatore controllato in tensione (VCO) e l'uscita del VCO è collegata a uno degli ingressi di un rilevatore di fase che è mostrato di seguito nello schema a blocchi di base. Quando questi due dispositivi si alimentano l'un l'altro, si forma il loop.

SCHEMA DI BASE DEL LOOP BLOCCATO IN FASE

Schema a blocchi e principio di funzionamento di PLL

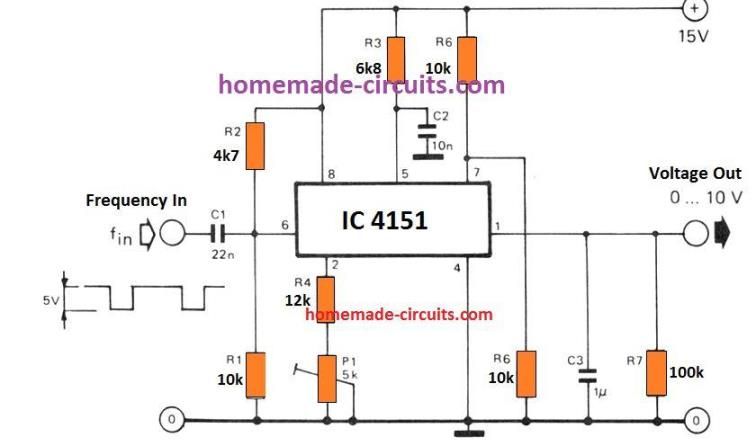

Il circuito ad aggancio di fase è costituito da un rilevatore di fase, a oscillatore controllato in tensione e, tra di loro, viene fissato un filtro passa basso. Il segnale di ingresso 'Vi' con una frequenza di ingresso 'Fi' è concesso da un rilevatore di fase. Fondamentalmente il rilevatore di fase è un comparatore che confronta la frequenza di ingresso fi attraverso la frequenza di feedback fo. L'uscita del rilevatore di fase è (fi + fo) che è una tensione CC. Il rilevatore fuori fase, ovvero la tensione CC viene immessa nel filtro passa basso (LPF) rimuove il rumore ad alta frequenza e produce un livello CC costante, ovvero Fi-Fo. La Vf è anche una caratteristica dinamica del PLL.

Schema a blocchi PLL

L'uscita del filtro passa basso, cioè il livello DC, viene trasmessa al VCO. Il segnale di ingresso è direttamente proporzionale alla frequenza di uscita del VCO (fo). Le frequenze di ingresso e di uscita vengono confrontate e regolate attraverso il ciclo di feedback fino a quando la frequenza di uscita è uguale alla frequenza di ingresso. Quindi, il PLL funziona come free running, capture e phase lock.

Quando non è applicata alcuna tensione di ingresso, si dice che sia uno stadio a funzionamento libero. Non appena la frequenza di ingresso applicata al VOC cambia e produce una frequenza di uscita per il confronto, viene chiamata stadio di cattura. La figura seguente mostra lo schema a blocchi del PLL.

Rilevatore di loop ad aggancio di fase

Il rilevatore ad anello ad aggancio di fase confronta la frequenza di ingresso e la frequenza di uscita del VCO per produrre una tensione CC che è direttamente proporzionale alla distinzione di fase delle due frequenze. I segnali analogici e digitali vengono utilizzati nel loop ad aggancio di fase. La maggior parte dei file PLL monolitici circuiti integrati utilizzare un rilevatore di fase analogico e la maggior parte dei rilevatori di fase sono di tipo digitale. Un circuito a doppia miscela bilanciata viene comunemente utilizzato nei rivelatori di fase analogici. Di seguito sono riportati alcuni rilevatori di fase comuni:

Rilevatore di fase OR esclusivo

Un esclusivo rilevatore di fase OR è il tipo CMOS IC 4070. Le frequenze di ingresso e di uscita vengono applicate al rilevatore di fase EX OR. Per ottenere l'uscita alta almeno un ingresso dovrebbe essere basso e le altre condizioni di uscita sono basse come mostrato nella tabella di verità sottostante. Consideriamo la forma d'onda, le frequenze di ingresso e di uscita, cioè fi e fo hanno una differenza di fase di 0 gradi. Quindi la tensione di uscita CC del comparatore sarà una funzione della differenza di fase tra i due ingressi.

| essere | fo | Vdc |

Basso | Basso | Basso |

Basso | alto | alto |

alto | Basso | alto |

Alto | Alto | Basso |

Le funzioni della differenza di fase tra fi e fo sono come mostrato nel grafico della tensione di uscita CC. Se il rilevatore di fase è di 180 gradi, la tensione di uscita è massima. Se entrambe le frequenze di ingresso e di uscita sono onde quadre, vengono utilizzati questi tipi di rilevatori di fase.

Rilevatore di fase OR esclusivo

Rilevatore di fase Edge Trigger

Un rilevatore di fase edge trigger viene utilizzato quando le frequenze di ingresso e uscita sono in forma d'onda a impulsi, che è inferiore al 50% del ciclo di lavoro. Il flip flop R-S viene utilizzato per i rilevatori di fase, come mostrato nella figura seguente. A da R-S ciabatte infradito , le due porte NOR sono incrociate. L'uscita del rilevatore di fase può cambiare il suo stato logico attivando il flip flop R-S. Il fronte positivo delle frequenze di ingresso e di uscita può modificare l'uscita del rilevatore di fase.

Rilevatore di fase Edge Trigger

Rilevatore di fase monolitico

Un rilevatore di fase monolitico è di tipo CMOS, cioè IC 4044. È altamente compensato dalla sensibilità armonica e i problemi del ciclo di lavoro vengono abbandonati poiché il circuito può rispondere solo alla transizione del segnale di ingresso. Nelle applicazioni critiche, è il rilevatore di fase più febbrile. Le variazioni indipendenti dell'ampiezza sono libere dall'errore di fase, dalla tensione dell'errore di uscita e dal ciclo di lavoro delle forme d'onda di ingresso.

Applicazioni di Phase-Locked Loop

- Reti di demodulazione FM per operazioni FM

- È usato in controlli di velocità del motore e filtri di tracciamento.

- Viene utilizzato nella decodifica del cambio di frequenza per le frequenze portanti della demodulazione.

- Viene utilizzato in tempo per convertitori digitali.

- Viene utilizzato per la riduzione del jitter, la soppressione dello skew, il ripristino del clock.

Questo riguarda il principio di funzionamento e funzionamento del loop ad aggancio di fase e le sue applicazioni. Ci auguriamo che le informazioni fornite nell'articolo siano utili per sapere qualcosa sul progetto e capirlo. Inoltre, se hai domande su questo articolo e su progetti elettrici ed elettronici puoi commentare nella sezione sottostante. Ecco una domanda per te, qual è il modo migliore per simulare il PLL per la stabilità?

Crediti fotografici:

- Diagramma a blocchi di PLL circuiti oggi

- Rilevatore di fase OR esclusivo sanfoundry

- Rilevatore di fase Edge Trigger LEARNABOUT-ELECTRONICS

![Diodi a contatto puntuale [Storia, costruzione, circuito di applicazione]](https://electronics.jf-parede.pt/img/electronics-tutorial/38/point-contact-diodes-history-construction-application-circuit-1.jpg)