L'unità di controllo è il componente principale di un'unità di elaborazione centrale (CPU) nei computer che può dirigere le operazioni durante l'esecuzione di un programma tramite il processore /computer. La funzione principale dell'unità di controllo è quella di recuperare ed eseguire istruzioni dalla memoria di un computer. Riceve le istruzioni / informazioni in ingresso dall'utente e le converte in segnali di controllo , che vengono poi consegnati alla CPU per un'ulteriore esecuzione. È incluso come parte dell'architettura Von Neumann sviluppata da John Neumann. È responsabile della fornitura dei segnali di temporizzazione e dei segnali di controllo e dirige l'esecuzione di un programma da parte della CPU. È incluso come parte interna della CPU nei computer moderni. Questo articolo descrive le informazioni complete sull'unità di controllo.

Cos'è l'unità di controllo?

Il componente che riceve il segnale di ingresso / informazione / istruzione dall'utente e lo converte in segnali di controllo per l'esecuzione nella CPU. Controlla e dirige la memoria principale, l'unità aritmetica e logica (ALU), i dispositivi di input e output ed è anche responsabile delle istruzioni che vengono inviate alla CPU di un computer. Recupera le istruzioni dal file memoria principale di un processore e inviato al registro delle istruzioni del processore, che contiene il contenuto del registro.

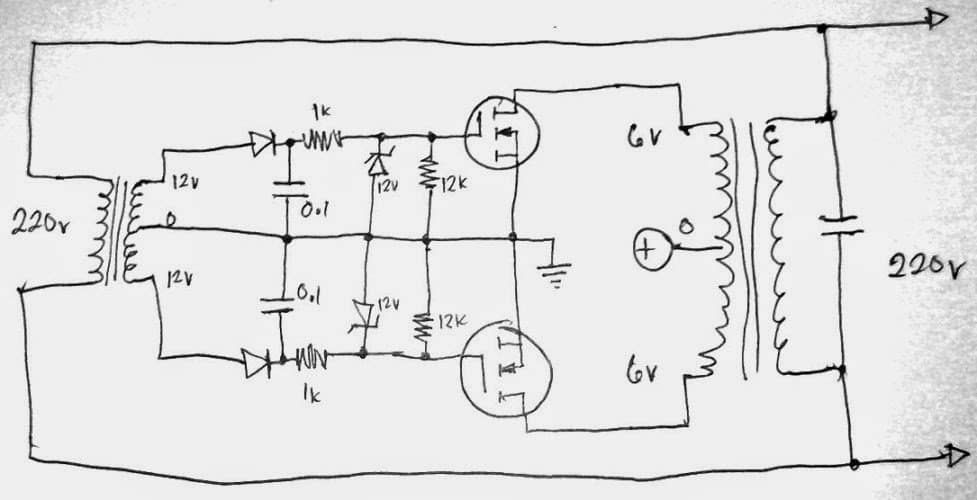

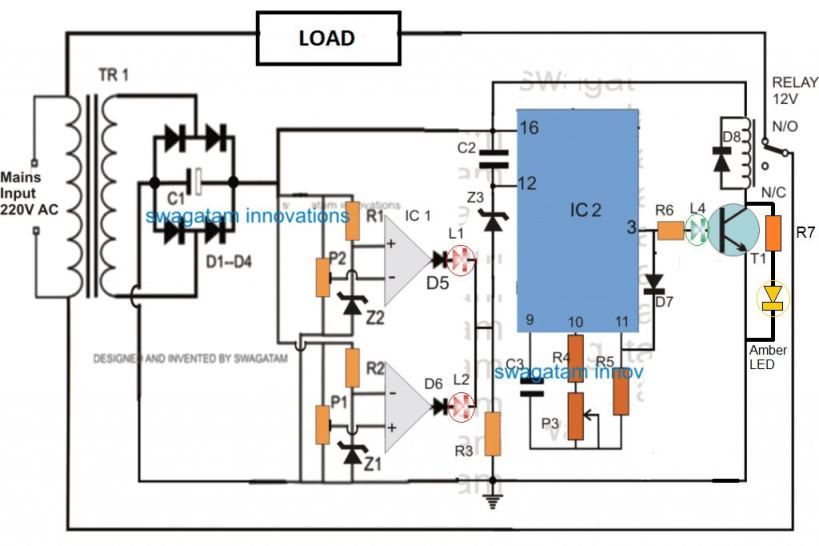

Schema a blocchi dell'unità di controllo

L'unità di controllo converte l'ingresso in segnali di controllo e quindi inviati al processore e dirige l'esecuzione di un programma. Le operazioni che devono essere eseguite sono dirette dal processore sul computer. Principalmente unità di elaborazione centrale (CPU) e Unità di elaborazione grafica (GPU) richiedono un'unità di controllo come parte interna. Lo schema a blocchi della centralina è mostrato sopra.

Componenti di un'unità di controllo

I componenti di questa unità sono istruzioni registri , segnali di controllo all'interno della CPU, segnali di controllo al / dal bus, bus di controllo, flag di ingresso e segnali di clock.

I componenti dell'unità di controllo cablata sono il registro delle istruzioni (contiene il codice operativo e il campo dell'indirizzo), l'unità di temporizzazione, lo stato di controllo Generatore , matrice di generazione del segnale di controllo e decodificatore di istruzioni.

I componenti dell'unità di controllo programmata Micro sono il generatore di indirizzi successivo, un registro di indirizzo di controllo, memoria di controllo e registro di dati di controllo.

Funzioni

Il funzioni della centralina include il seguente.

- Dirige il flusso della sequenza di dati tra il processore e altri dispositivi.

- Può interpretare le istruzioni e controllare il flusso di dati nel processore.

- Genera la sequenza dei segnali di controllo dalle istruzioni ricevute o dai comandi dal registro delle istruzioni.

- Ha la responsabilità di controllare le unità di esecuzione come ALU, buffer di dati e registri nella CPU di un computer.

- Ha la capacità di recuperare, decodificare, gestire l'esecuzione e memorizzare i risultati.

- Non può elaborare e memorizzare i dati

- Per trasferire i dati, comunica con i dispositivi di input e output e controlla tutte le unità del computer.

Progettazione dell'unità di controllo

Il design di questo può essere fatto usando due tipi di unità di controllo che includono quanto segue.

- Basato su cavo

- Basato su microprogrammi (a livello singolo e a due livelli)

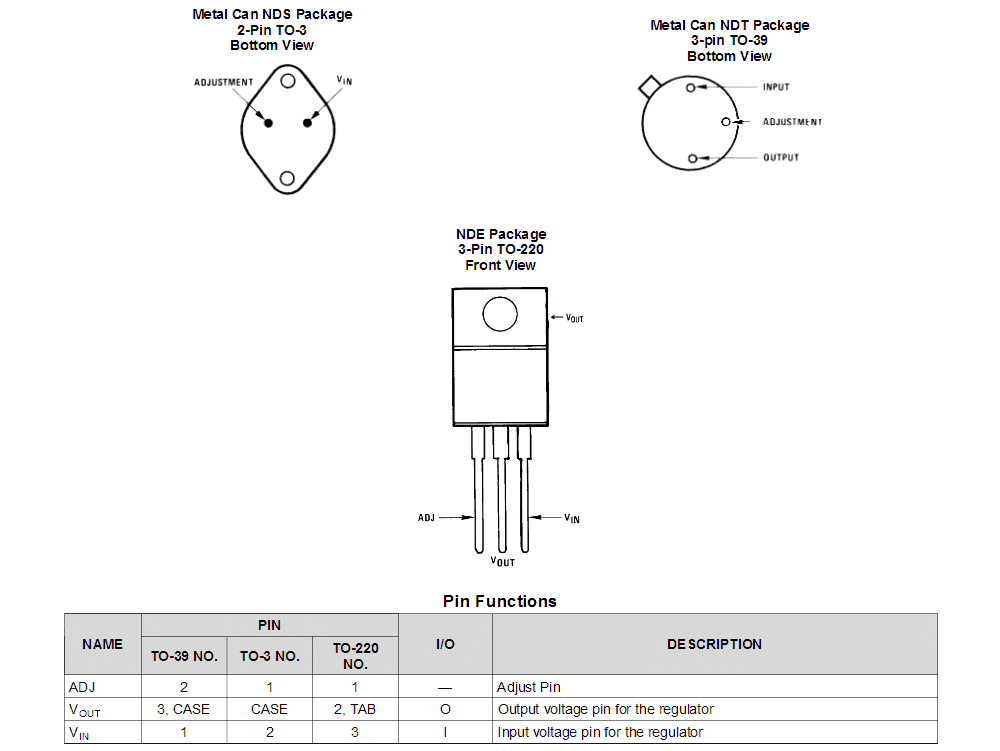

Unità di controllo cablata

Il design di base di un'unità di controllo cablata è mostrato sopra. In questo tipo, i segnali di controllo sono generati da un hardware speciale circuito logico senza alcun cambiamento nella struttura del circuito. In questo, il segnale generato non può essere modificato per l'esecuzione nel processore.

I dati di base di un codice operativo (il codice di operazione di un'istruzione viene inviato al decodificatore dell'istruzione per la decodifica. L'istruzione decodificatore è l'insieme di decodificatori per decodificare diversi tipi di dati nel codice operativo. Ciò si traduce in segnali di uscita che contengono valori di segnali attivi che vengono forniti come input al generatore di matrici per generare segnali di controllo per l'esecuzione di un programma da parte del processore del computer.

Unità di controllo basata su cablaggio

Il generatore di matrice fornisce gli stati dell'unità di controllo e i segnali in uscita dal processore (segnali di interrupt). Matrix è costruito come matrice logica programmabile . I segnali di controllo generati dal generatore di matrici vengono forniti come input alla successiva matrice del generatore e si combinano con i segnali di temporizzazione dell'unità di temporizzazione che contiene modelli rettangolari.

Per il recupero di una nuova istruzione, l'unità di controllo si trasforma in una fase iniziale per l'esecuzione di una nuova istruzione. L'unità di controllo rimane nella fase iniziale o nella prima fase finché i segnali di temporizzazione, i segnali di ingresso e gli stati di istruzione di un computer rimangono invariati. Il cambiamento nello stato della centralina può essere aumentato se c'è qualche cambiamento in uno qualsiasi dei segnali generati.

Quando si verifica un segnale esterno o un interrupt, l'unità di controllo passa allo stato successivo ed esegue l'elaborazione del segnale di interrupt. I flag e gli stati vengono utilizzati per selezionare gli stati desiderati per eseguire il ciclo di esecuzione dell'istruzione.

Nell'ultimo stato, l'unità di controllo preleva l'istruzione successiva e invia l'uscita al contatore del programma, quindi al registro dell'indirizzo di memoria, al registro del buffer e quindi al registro dell'istruzione per leggere l'istruzione. Infine, se l'ultima istruzione (che viene recuperata dall'unità di controllo) è istruzione di fine, allora si passa allo stato operativo del processore e attende fino a quando l'utente non dirige il programma successivo.

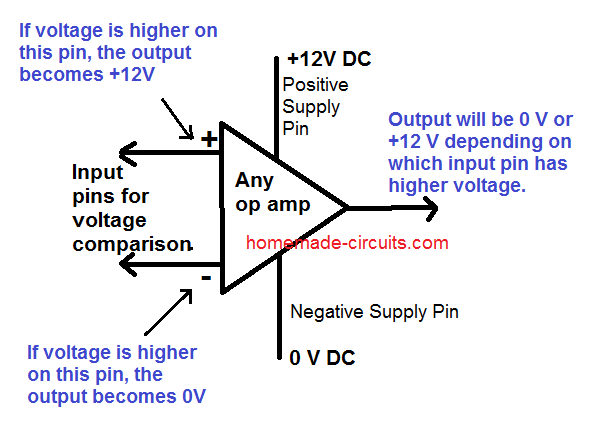

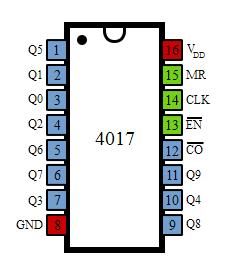

Unità di controllo micro programmata

In questo tipo, la memoria di controllo viene utilizzata per memorizzare i segnali di controllo che vengono codificati durante l'esecuzione di un programma. Il segnale di controllo non viene generato immediatamente e decodificato perché il microprogramma memorizza il campo indirizzo nella memoria di controllo. L'intero processo è un unico livello.

Le micro operazioni vengono eseguite per l'esecuzione delle micro istruzioni nel programma. Sopra è riportato lo schema a blocchi della centralina Micro programmata. Dal diagramma, l'indirizzo della microistruzione è ottenuto dal registro degli indirizzi della memoria di controllo. Tutte le informazioni della centrale sono memorizzate in modo permanente nella memoria di controllo chiamata ROM.

Unità di controllo basata su microprogrammata

La microistruzione dalla memoria di controllo è mantenuta dal registro di controllo. Poiché la microistruzione è sotto forma di parola di controllo (contiene valori di controllo binari), è necessario eseguire 1 o più micro operazioni per l'elaborazione dei dati.

Durante l'esecuzione delle microistruzione, il generatore di indirizzi successivo ha calcolato l'indirizzo successivo della microistruzione e quindi invia al registro dell'indirizzo di controllo per leggere la microistruzione successiva.

La sequenza di micro-operazioni di un micro-programma viene eseguita dal successivo generatore di indirizzi e funge da sequenziatore di microprogrammi per ottenere l'indirizzo della sequenza, cioè letto dalla memoria di controllo.

Codice Verilog per l'unità di controllo

Il codice Verilog per l'unità di controllo è mostrato di seguito.

`include' prj_definition.v '

modulo CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_R1 RF)

// Segnali di uscita

// Uscite per il file di registro

output [`DATA_INDEX_LIMIT: 0] RF_DATA_W

output [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

uscita RF_READ, RF_WRITE

// Uscite per ALU

output [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

output [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Uscite per la memoria

output [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

uscita MEM_READ, MEM_WRITE

// Segnali di ingresso

input [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

ingresso ZERO, CLK, RST

// Segnale Inout

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Reti di stato

wire [2: 0] proc_state

// contiene il valore del contatore del programma, memorizza l'istruzione corrente, il registro del puntatore dello stack

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

sempre @ (posedge CLK)

inizio

se (RST)

stato<= RST

altro

stato<= next_state

fine

sempre @ (stato)

inizio

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

case (stato)

`PROC_FETCH: inizio

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

fine

`PROC_DECODE: inizio

next_state = `` PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

fine

`PROC_EXE: inizia

next_state = `` PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

fine

`PROC_MEM: inizio

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

fine

`PROC_WB: inizio

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

fine

endcase

fine

endmodule

modulo PROC_SM (STATE, CLK, RST)

// elenco di input

ingresso CLK, RST

// elenco di output

uscita [2: 0] STATE

// elenco di input

ingresso CLK, RST

// elenco di output

STATO di uscita

reg [2: 0] STATE

stato reg [1: 0]

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`definire PROC_FETCH 3’h0

`definire PROC_DECODE 3’h1

`definire PROC_EXE 3’h2

`definire PROC_MEM 3’h3

`definire PROC_WB 3’h4

// iniziazione di stato

iniziale

inizio

stato = 2’bxx

next_state = `PROC_FETCH

fine

// resetta la gestione del segnale

sempre @ (posedge RST)

inizio

state = `PROC_FETCH

next_state = `PROC_FETCH

fine

sempre @ (posedge CLK)

inizio

state = next_state

fine

sempre @ (stato)

inizio

if (state === `PROC_FETCH)

inizio

next_state = `PROC_DECODE

istruzione_stampa (INST_REG)

fine

if (state === `PROC_DECODE)

inizio

next_state = `` PROC_EXE

fine

if (state === `PROC_EXE)

inizio

next_state = `` PROC_MEM

istruzione_stampa (SP_REF)

fine

if (state === `PROC_MEM)

inizio

next_state = `PROC_WB

fine

if (state === `PROC_WB)

inizio

next_state = `PROC_FETCH

istruzione_stampa (PC_REG)

fine

fine

task print_istruzione

input [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] codice operativo

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] immediato reg [25: 0] indirizzo

inizio

// analizza l'istruzione

// tipo R

{codice operativo, rs, rt, rd, shamt, funct} = inst

// Io digito

{codice operativo, rs, rt, immediato} = inst

// tipo J

{codice operativo, indirizzo} = inst

$ write ('@% 6dns -> [0X% 08h]', $ time, inst)

case (opcode) // R-Type

6'h00: inizio

case (funzione)

6’h20: $ write ('add r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h22: $ write ('sub r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2c: $ write ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h24: $ write ('and r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h25: $ write ('or r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h27: $ write ('nor r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2a: $ write ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h00: $ write ('sll r [% 02d],% 2d, r [% 02d]', rs, shamt, rd)

6’h02: $ write ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6’h08: $ write ('jr r [% 02d]', rs)

predefinito: $ write ('')

endcase

fine

// Io digito

6’h08: $ write ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h1d: $ write ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h0c: $ write ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediate)

6’h0d: $ write ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h0f: $ write ('lui r [% 02d], 0X% 04h', rt, immediato)

6’h0a: $ write ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h04: $ write ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h05: $ write ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

6’h23: $ write ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediate)

6’h2b: $ write ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immediato)

// J-Type

6’h02: $ write ('jmp 0X% 07h', indirizzo)

6’h03: $ write ('jal 0X% 07h', indirizzo)

6’h1b: $ write ('push')

6’h1c: $ write ('pop')

predefinito: $ write ('')

endcase

$ write (' n')

fine

ultimo compito

modulo finale

Domande frequenti

1). Qual è il lavoro di un'unità di controllo?

Il lavoro dell'unità di controllo è dirigere il flusso di dati o istruzioni per l'esecuzione da parte del processore di un computer. Controlla, gestisce e coordina memoria principale, ALU, registri, unità di input e output. Recupera le istruzioni e genera segnali di controllo per l'esecuzione.

2). Qual è la memoria di controllo?

La memoria di controllo è solitamente RAM o ROM per memorizzare l'indirizzo e i dati del registro di controllo.

3). Cos'è l'unità di controllo Wilkes?

Il sequenziale e circuiti combinatori della centralina cablata vengono sostituite dalla centralina Wilkes. Utilizza un'unità di memoria per memorizzare le sequenze di istruzioni di un microprogramma.

4). Cos'è un'unità di controllo cablata?

L'unità di controllo cablata genera i segnali di controllo passando da uno stato all'altro in ogni impulso di clock senza alcun cambiamento fisico nel circuito. La generazione dei segnali di controllo dipende dal registro delle istruzioni, dal decodificatore e dai segnali di interrupt.

5). Qual è la memoria di controllo?

Le informazioni dell'unità di controllo o dei dati vengono memorizzati temporaneamente o permanentemente nella memoria di controllo.

La memoria di controllo è di due tipi. Sono Random Access Memory (RAM) e Read-Only Memory (ROM).

Quindi, si tratta di definizione, componenti, design, diagramma, funzioni e tipi di unità di controllo . Ecco una domanda per te: 'Qual è lo scopo del registro degli indirizzi di controllo?'