Il post discute la funzione di pinout e altre importanti specifiche dell'IC 4043. Impariamo a conoscere la scheda tecnica completa di questo chip molto interessante.

Pinout Datasheet di IC 4043

Tecnicamente l'IC 4043 è un latch quad set / reset (R / S) con 3 uscite di stato logico.

Per essere più precisi, questo chip ha 4 serie di ingressi (ovvero 8 piedinature degli ingressi) e 4 uscite singole corrispondenti.

I 4 set di ingressi sono costituiti da 4 coppie di ingressi set / reset.

Per ogni set / reset abbiamo un'uscita corrispondente.

Tutti questi ingressi di reset impostati rispondono a segnali logici alti, creando un effetto bistabile alle corrispondenti piedinature di uscita.

Flip / Flop bistabile

Bistabile si riferisce all'azione del flip flop, in altre parole un impulso alto all'ingresso 'impostato' rende l'uscita corrispondente alta dal suo stato basso originale e un ingresso alto all'ingresso di ripristino ripristina lo stato precedente dallo stato alto allo stato basso.

Quindi fondamentalmente per rendere alte le uscite corrispondenti, dobbiamo applicare un alto ai loro ingressi 'impostati' e per rendere nuovamente basse le uscite dobbiamo semplicemente applicare un altro alto ai loro ingressi di ripristino.

Il funzionamento dei pinout di ingresso e uscita è così semplice.

Oltre a questo, l'IC ha un altro interessante pinout di ingresso OE che è un pinout di abilitazione dell'uscita comune.

Funzione Set / Reset

Per abilitare le azioni di impostazione / ripristino sopra spiegate nell'IC, questo ingresso OE deve essere collegato con logica alta o semplicemente con Vdd (voto di alimentazione).

Nella situazione precedente l'uscita è consentita con il funzionamento del flip flop specificato.

Se l'ingresso OE è collegato a massa, l'uscita si blocca e produce una risposta ad alta impedenza, che non mostra né un'uscita bassa né un'uscita alta, ma blocca l'ingresso in uno stato di blocco che non risponde, da cui il nome 3 uscita a stato logico.

Pertanto, l'ingresso OE può essere utilizzato per arrestare il funzionamento dell'IC, se necessario per una particolare applicazione.

L'IC funziona al meglio con tensioni di alimentazione da 5 a 15 V.

Riassumiamo le funzioni e le specifiche del pinout di input output dell'IC 4043 con i seguenti dati:

- Da 1Q a 4Q (Pin: 2, 9, 10, 1) Uscita latch bufferizzata a 3 stati

- Ingresso di reset da 1R a 4R (pin: 3, 7, 11, 15) (attivo HIGH)

- Ingresso da 1S a 4S (pin: 4, 6, 12, 14) (attivo HIGH)

- Ingresso di abilitazione uscita comune OE (Pin: 5)

- VSS (Pin: 8) tensione di alimentazione di terra

- N.C. (Pin: 13) non connesso

- Tensione di alimentazione VDD (Pin: 16)

Ulteriori aggiornamenti:

In questo post cerchiamo di capire il funzionamento dell'IC 4043 e dell'IC 4044 studiando le varie specifiche, datasheet dei dispositivi e loro disposizione dei pinout.

Fondamentalmente entrambe le varianti sono quadricromia CMOS a 3 stati R / S o Reset / Set Latches. Quad mezzi aventi 4 uscite che possono essere impostate o bloccate con un alto logico tramite un segnale di ingresso di controllo, o ripristinate a zero logico da un segnale di ingresso successivo.

La funzionalità a 3 stati consente di controllare i circuiti integrati utilizzando 3 logiche

Il principio di funzionamento di base di IC 4043 e IC 4044 è lo stesso di sopra, l'unica differenza è che IC 4043B sono quad accoppiati a 3 stati NÉ Latch e IC 4044B sono a 3 stati con accoppiamento incrociato quadruplo NAND Fermo.

Diagramma di piedinatura

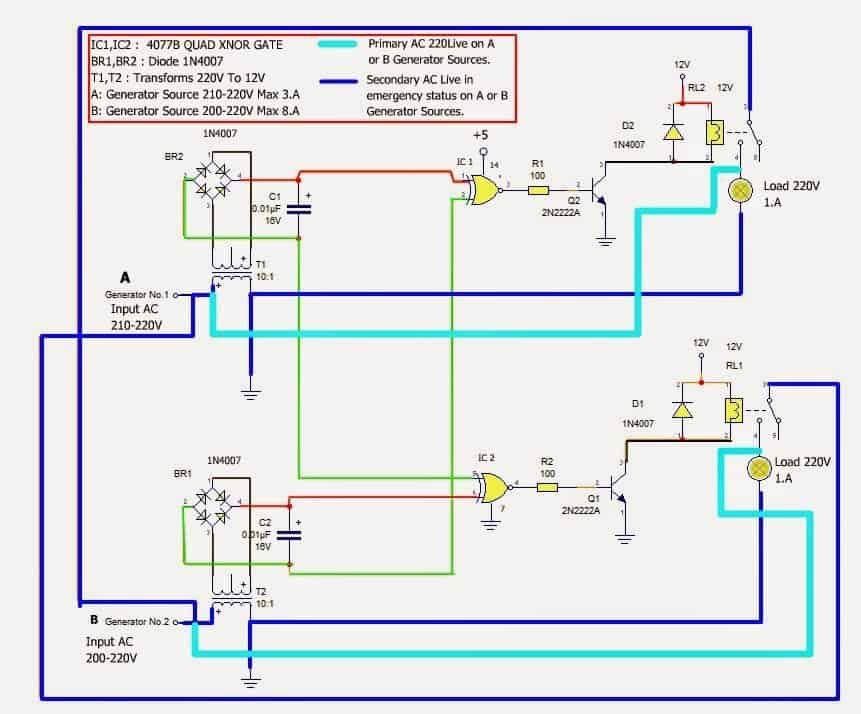

I seguenti diagrammi di pinout dei circuiti integrati mostrano la struttura interna ei dettagli di pinout dei dispositivi:

Negli schemi sopra possiamo vedere che ciascuno dei tipi ha 4 latch con un'uscita e 2 singoli ingressi RESET / SET. La funzione del pin ENABLE per tutti gli ingressi SET / RESET è identica.

Una logica HIGH sul pin ENABLE consente agli stati di latch di connettersi con le uscite pertinenti, una logica bassa o 0 disconnette gli stati di latch dalle loro uscite causando un circuito aperto completo sulle uscite.

NOR Latch, NAND Latch Diagrammi logici equivalenti

I seguenti diagrammi mostrano i latch equivalenti sotto forma di latch NOR e NAND, che sono presenti all'interno di ciascuno dei 4 latch dei singoli circuiti integrati.

Come possiamo vedere, ciascuno dei blocchi di latch è controllato utilizzando 3 ingressi di controllo logico, ovvero SET, RESET e ENABLE, quindi l'uscita dipende da questi 3 stati di ingresso. La tabella di verità per questi 3 stati logici può essere appresa dal seguente diagramma:

Nella tabella di verità sopra, la forma completa dei vari alfabeti simbolici abbreviati può essere intesa come indicato di seguito: S = SET Pin R = RESET Pin E = ENABLE Pin Q = OUTPUT Pin OC = Circuito aperto NC = Nessuna modifica

Le caratteristiche principali dell'IC 4043 e dell'IC 4044 sono riassunte di seguito:

Pratica simulazione di lavoro di base dei pin SET / RESET e ENABLE

Descrizione di lavoro

Dalla GIF di simulazione sopra possiamo capire il funzionamento dei moduli quad latch con i seguenti punti:

Quando il pin SET è applicato con un'alimentazione positiva, l'uscita diventa alta e diventa bloccata anche se il potenziale positivo viene rimosso dal pin SET, come indicato dal LED rosso (polarizzato in avanti).

Quando il pin RESET viene applicato con un impulso positivo, il latch si rompe e l'uscita diventa BASSA permanentemente anche se il positivo viene rimosso dal pin RESET. Ciò è indicato dall'illuminazione del LED blu.

Le operazioni di cui sopra possono essere implementate solo fintanto che il pin ENABLE dell'IC è ad un potenziale di alimentazione positivo. Quando è collegata a un potenziale negativo o di terra, l'uscita del latch diventa aperta e non risponde alle operazioni di SET / RESET.

Precedente: Circuito timer programmabile giorno della settimana Avanti: IC 4033 Pinout, foglio dati, applicazione