Il transistor a semiconduttore in ossido di metallo o transistor MOS è un elemento fondamentale nei chip logici, nei processori e nelle moderne memorie digitali. È un dispositivo a vettore maggioritario, in cui la corrente all'interno di un canale conduttore tra la sorgente e il pozzo è modulata da una tensione applicata al gate. Questo transistor MOS svolge un ruolo chiave in vari circuiti integrati analogici e a segnale misto. Questo transistor è abbastanza adattabile, quindi funziona come un amplificatore, un interruttore o un resistore . non transistor sono classificati in due tipi PMOS e NMOS. Quindi, questo articolo discute una panoramica di Transistor NMOS – fabbricazione, circuito e lavorazione.

Cos'è un transistor NMOS?

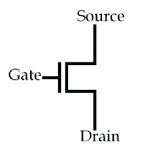

Un transistor NMOS (semiconduttore di ossido di metallo a canale n) è un tipo di transistor in cui vengono utilizzati droganti di tipo n nella regione di gate. Una tensione positiva (+ve) sul terminale di gate accende il dispositivo. Questo transistor è utilizzato principalmente in CMOS (semiconduttore di ossido di metallo complementare) e anche in logica e chip di memoria. Rispetto al transistor PMOS, questo transistor è molto più veloce, quindi è possibile posizionare più transistor su un singolo chip. Il simbolo del transistor NMOS è mostrato di seguito.

Come funziona il transistor NMOS?

Il funzionamento del transistor NMOS è; quando il transistor NMOS riceve una tensione non trascurabile, forma un circuito chiuso, il che significa che la connessione dal terminale di source al drain funziona come un filo. Quindi la corrente scorre dal terminale di gate alla sorgente. Allo stesso modo, quando questo transistor riceve una tensione di circa 0 V, forma un circuito aperto, il che significa che la connessione dal terminale di source al drain verrà interrotta, quindi la corrente fluirà dal terminale di gate al drain.

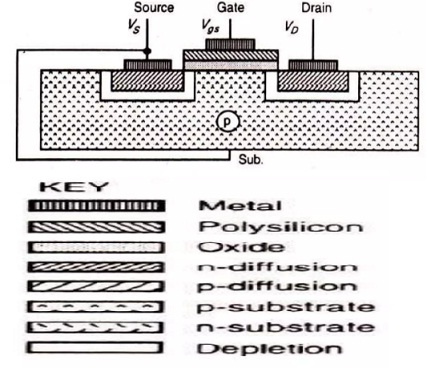

Sezione trasversale del transistor NMOS

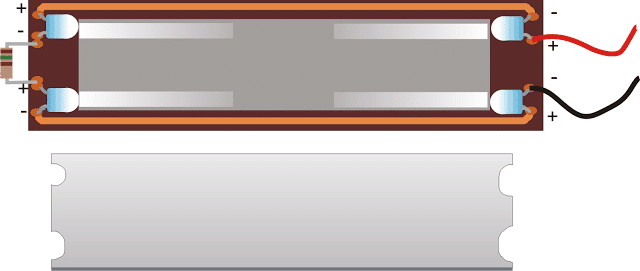

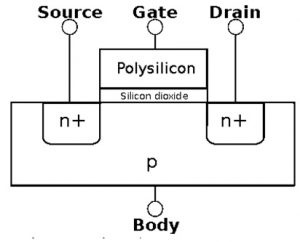

Generalmente, un transistor NMOS è semplicemente costruito con un corpo di tipo p da due regioni semiconduttrici di tipo n che sono adiacenti al gate noto come source e drain. Questo transistor ha un gate di controllo che controlla il flusso di elettroni tra i terminali source e drain.

In questo transistor, poiché il corpo del transistor è collegato a terra, le giunzioni PN di source e drain verso il corpo sono polarizzate inversamente. Se la tensione al terminale di gate viene aumentata, un campo elettrico inizierà ad aumentare e attirerà elettroni liberi alla base dell'interfaccia Si-SiO2.

Una volta che la tensione è sufficientemente alta, gli elettroni finiscono per riempire tutti i buchi e una sottile regione sotto il gate nota come canale verrà invertita per funzionare come un semiconduttore di tipo n. Ciò creerà una corsia conduttrice dal terminale sorgente allo scarico consentendo il flusso di corrente, quindi il transistor verrà acceso. Se il terminale di gate è collegato a terra, non scorre corrente nella giunzione polarizzata inversa, quindi il transistor verrà spento.

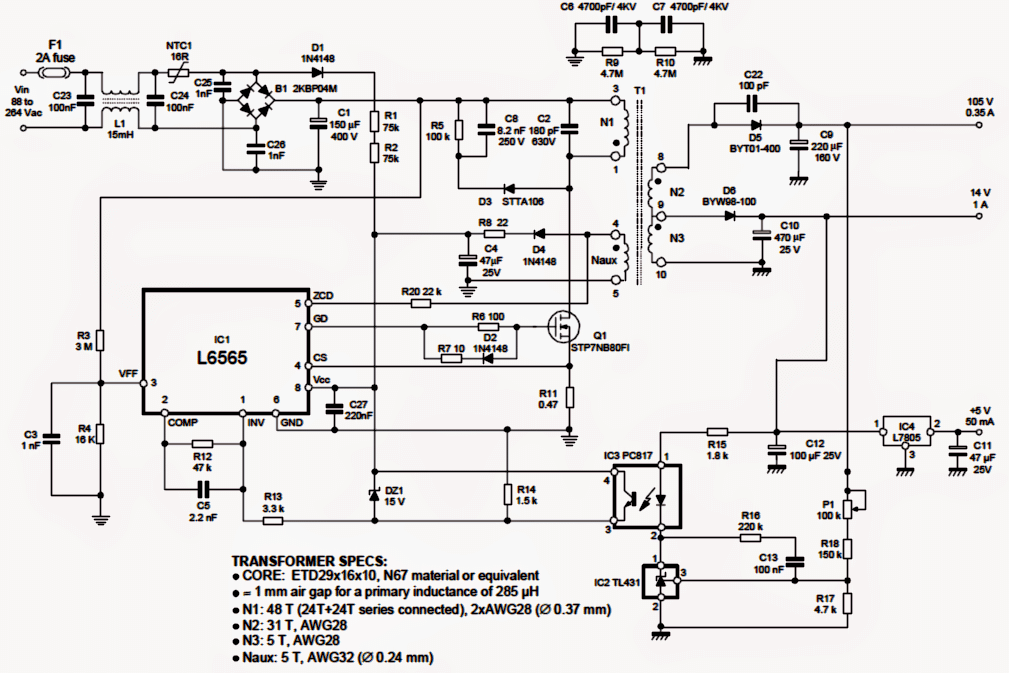

Circuito a transistor NMOS

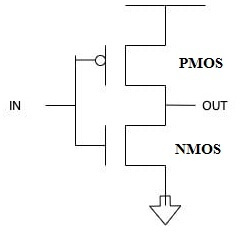

Di seguito è mostrato il design del gate NOT che utilizza transistor PMOS e NMOS. Per progettare una porta NOT, dobbiamo combinare transistor pMOS e nMOS collegando un transistor pMOS alla sorgente e un transistor nMOS a terra. Quindi il circuito sarà il nostro primo esempio di transistor CMOS.

La porta NOT è un tipo di porta logica che genera un ingresso invertito come uscita. Questo gate è anche chiamato inverter. Se l'ingresso è '0', l'uscita invertita sarà '1'.

Quando l'ingresso è zero, va al transistor pMOS in alto e in basso al transistor nMOS in basso. Una volta che il valore di ingresso '0' raggiunge il transistor pMOS, viene invertito in '1'. quindi, la connessione verso la sorgente viene interrotta. Quindi questo genererà un valore logico '1' se anche la connessione verso lo scarico (GND) è chiusa. Sappiamo che il transistor nMOS non invertirà il valore di ingresso, quindi prende il valore zero così com'è e creerà un circuito aperto allo scarico. Quindi, viene generato un valore logico uno per il gate.

Allo stesso modo, se il valore di ingresso è '1', questo valore viene inviato a entrambi i transistor nel circuito sopra. Una volta che il valore '1' riceve il transistor pMOS, verrà invertito in una 'o'. di conseguenza, la connessione verso la sorgente è aperta. Una volta che il transistor nMOS riceve il valore '1, non verrà invertito. quindi, il valore di input rimane uguale a uno. Una volta ricevuto un valore dal transistor nMOS, la connessione verso GND viene chiusa. Quindi genererà uno '0' logico come output.

Processo di fabbricazione

Ci sono molti passaggi coinvolti nel processo di fabbricazione del transistor NMOS. Lo stesso processo può essere utilizzato per i transistor PMOS e CMOS. Il materiale più utilizzato in questa fabbricazione è il polisilicio o il metallo. Le fasi del processo di fabbricazione passo-passo del transistor NMOS sono discusse di seguito.

Passo 1:

Un sottile strato di wafer di silicio viene trasformato in materiale di tipo P semplicemente drogando con materiale di boro.

Passo 2:

Uno spesso strato di Sio2 viene coltivato su un substrato di tipo p completo

Passaggio 3:

Ora la superficie è rivestita attraverso un fotoresist sullo spesso strato di Sio2.

Passaggio 4:

Successivamente, questo strato viene esposto alla luce UV con una maschera che descrive le regioni in cui deve avvenire la diffusione insieme ai canali del transistor.

Passaggio 5:

Queste regioni vengono incise reciprocamente con il sottostante Sio2 in modo che la superficie del wafer sia esposta all'interno della finestra definita attraverso la maschera.

Passaggio 6:

Il fotoresist residuo viene separato e lo strato sottile di Sio2 viene fatto crescere di 0,1 micrometri tipicamente sull'intera faccia del chip. Successivamente, il polisilicio si trova su questo per formare la struttura del gate. Un fotoresist viene posizionato sull'intero strato di polisilicio ed espone la luce ultravioletta in tutta la maschera2.

Passaggio 7:

Riscaldando il wafer alla massima temperatura, si ottengono le diffusioni e il passaggio del gas con impurità di tipo n desiderate come il fosforo.

Passaggio 8:

Uno spessore di un micrometro di biossido di silicio viene coltivato dappertutto e su di esso viene posizionato materiale fotoresist. Esporre la luce ultravioletta (UV) attraverso mask3 sulle regioni preferite di gate, le regioni di source e drain vengono incise per effettuare i tagli di contatto.

Passaggio 9:

Ora un metallo come l'alluminio viene posizionato sulla sua superficie larga un micrometro. Ancora una volta un materiale fotoresist viene fatto crescere su tutto il metallo ed esposto alla luce UV attraverso la maschera4 che è una forma incisa del design di interconnessione obbligatorio. La struttura NMOS finale è mostrata di seguito.

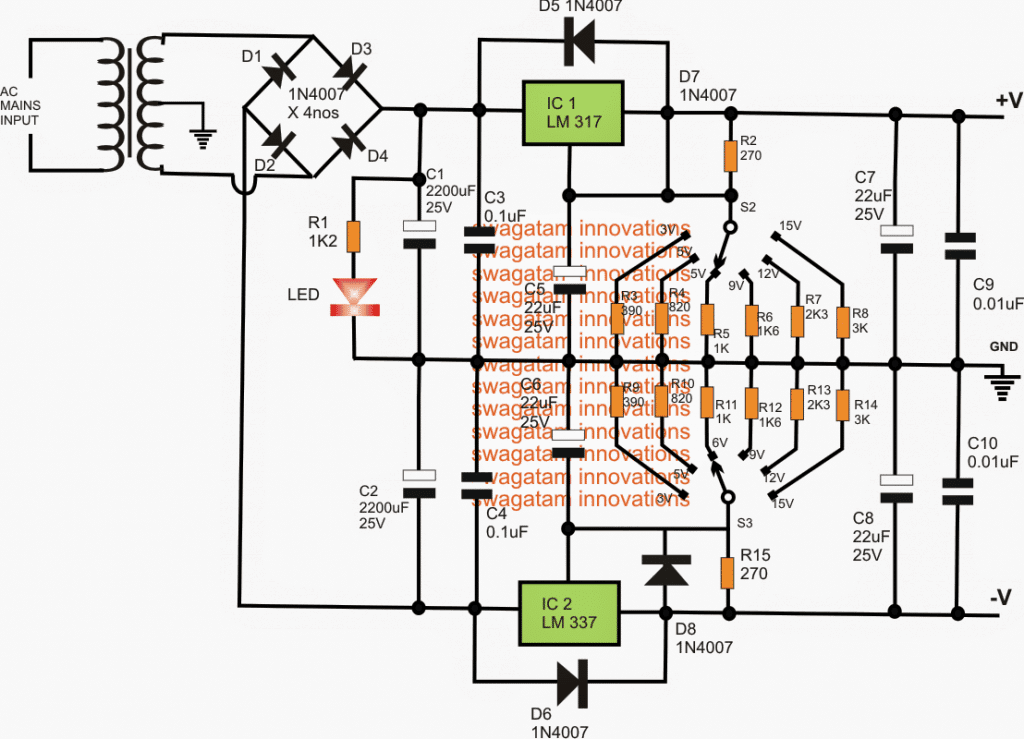

Transistor PMOS Vs NMOS

La differenza tra transistor PMOS e NMOS è discussa di seguito.

| Transistor PMOS | Transistor NMOS |

| Il transistor PMOS è l'acronimo di transistor semiconduttore a ossido di metallo a canale P. | Il transistor NMOS sta per transistor semiconduttore a ossido di metallo a canale N. |

| La sorgente e il drenaggio nei transistor PMOS sono semplicemente realizzati con semiconduttori di tipo n | La sorgente e il drenaggio nel transistor NMOS sono semplicemente realizzati con semiconduttori di tipo p. |

| Il substrato di questo transistor è realizzato con un semiconduttore di tipo n | Il substrato di questo transistor è realizzato con il semiconduttore di tipo p |

| La maggior parte dei portatori di carica in PMOS sono buchi. | La maggior parte dei portatori di carica in NMOS sono elettroni. |

| Rispetto a NMOS, i dispositivi PMOS non sono più piccoli. | I dispositivi NMOS sono abbastanza più piccoli rispetto ai dispositivi PMOS. |

| I dispositivi PMOS non possono essere commutati più velocemente rispetto ai dispositivi NMOS. | Rispetto ai dispositivi PMOS, i dispositivi NMOS possono essere commutati più velocemente. |

| Il transistor PMOS condurrà una volta fornita una bassa tensione al gate. | Il transistor NMOS condurrà una volta fornita un'alta tensione al gate. |

| Questi sono più immuni al rumore. | Rispetto ai PMOS, questi non sono immuni al rumore. |

| La tensione di soglia (Vth) di questo transistor è una quantità negativa. | La tensione di soglia (Vth) di questo transistor è una quantità positiva. |

Caratteristiche

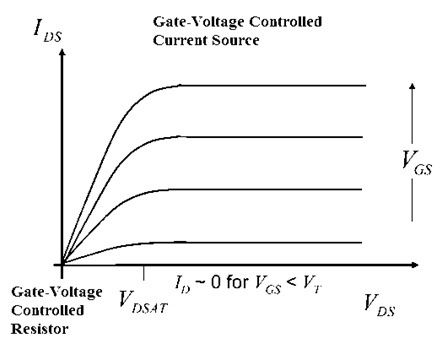

Il Caratteristiche IV del transistor NMOS sono mostrati di seguito. La tensione tra il gate e i terminali di source 'V GS ' e anche tra source e drain 'V DS '. Quindi, le curve tra I DS e v DS si ottengono semplicemente mettendo a terra il terminale della sorgente, impostando un valore VGS iniziale e spazzando V DS da '0' al valore di tensione CC più alto dato da V GG quando si calpesta il V GS valore da '0' a V GG . Quindi per V estremamente basso GS , l'io DS sono estremamente piccoli e avranno un andamento lineare. Quando il v GS il valore diventa alto, quindi I DS migliora e avrà la seguente dipendenza da V GS & IN DS ;

Se v GS è minore o uguale a V TH , quindi il transistor è in condizione OFF e si comporta come un circuito aperto.

Se v GS è maggiore di V TH , allora ci sono due modalità operative.

Se v DS è minore di V GS - IN TH , quindi il transistor funziona in modalità lineare e si comporta come una resistenza (R SU ).

IDS = u eff C bue W/L [(v GS - IN TH )IN DS – ½ v DS ^ 2]

Dove,

‘µeff’ è la mobilità effettiva del portatore di carica.

'COX' è la capacità dell'ossido di gate per ciascuna area unitaria.

W & L sono rispettivamente la larghezza e la lunghezza del canale. Il r SU il valore è semplicemente controllato dalla tensione del gate segue come;

R ACCESO = 1/pollice n C bue W/L [(v GS - IN TH )IN DS – ½ v DS ^ 2]

Se VDS è maggiore o uguale a V GS - IN TH , quindi il transistor funziona all'interno della modalità di saturazione

io DS = tu n C bue W/L [(v GS - IN TH )^2 (1+λ V DS ]

In questa regione, quando I DS è maggiore, allora la corrente dipende minimamente dalla V DS valore, tuttavia, il suo valore più alto è semplicemente controllato tramite VGS. La modulazione della lunghezza del canale 'λ' rappresenta l'aumento all'interno dell'IDS di un aumento all'interno del VDS nei transistor, a causa del pinch-off. Questo pizzicotto si verifica una volta che entrambi i V DS e v GS decidere sullo schema del campo elettrico vicino alla regione di drenaggio, cambiando così la direzione naturale dei portatori di carica di alimentazione. Questo effetto riduce la lunghezza del canale efficiente e aumenta I DS . Idealmente, 'λ' è equivalente a '0' in modo che I DS è totalmente indipendente dal V DS valore all'interno della regione di saturazione.

Quindi, questo è tutto una panoramica di un NMOS transistor – fabbricazione e circuito con funzionamento. Il transistor NMOS svolge un ruolo chiave nell'implementazione di porte logiche e altri circuiti digitali diversi. Questo è un circuito microelettronico utilizzato principalmente nella progettazione di circuiti logici, chip di memoria e nella progettazione CMOS. Le applicazioni più popolari dei transistor NMOS sono gli interruttori e gli amplificatori di tensione. Ecco una domanda per te, cos'è un transistor PMOS?