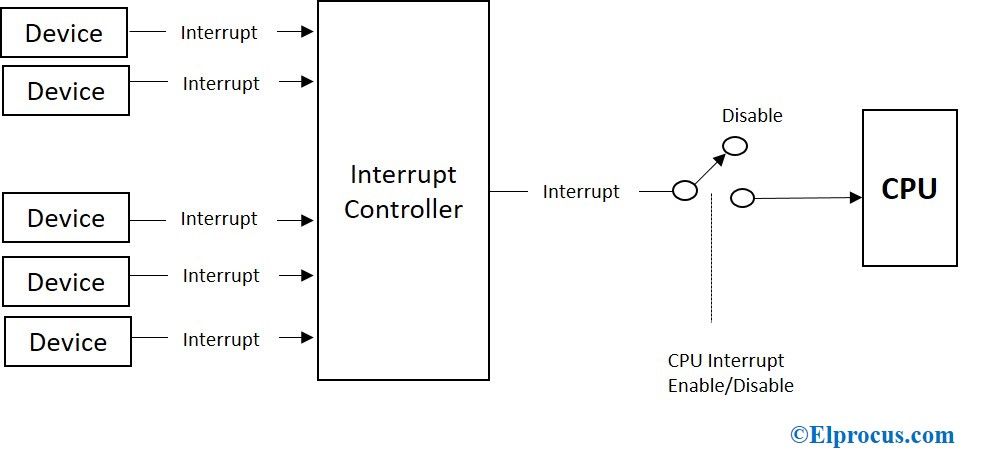

Aumentando la velocità di esecuzione del programma aumenta di conseguenza la velocità di il processore. Ci sono molti modi inventati, sia l'implementazione hardware che l'architettura software, per aumentare la velocità di esecuzione. È stato osservato che eseguendo le istruzioni contemporaneamente il tempo necessario per l'esecuzione può essere ridotto. Il concetto di parallelismo in programmazione è stato proposto. In base a ciò, è possibile eseguire più di un'istruzione per ciclo di clock. Questo concetto può essere praticato da un programmatore attraverso varie tecniche come Pipelining, più unità di esecuzione e più core . Tra tutti questi metodi di parallelismo, il pipelining è quello più comunemente praticato. Quindi come può essere eseguita un'istruzione nel metodo pipelining? Come aumenta la velocità di esecuzione?

Cos'è il pipelining?

Per comprendere il concetto di pipelining, esaminiamo il livello principale di come viene eseguito il programma. L'istruzione è il più piccolo pacchetto di esecuzione di un programma. Ogni istruzione contiene una o più operazioni. I processori scalari semplici eseguono una o più istruzioni per ciclo di clock, con ciascuna istruzione contenente una sola operazione. Le istruzioni vengono eseguite come una sequenza di fasi, per produrre i risultati attesi. Questa sequenza è data di seguito

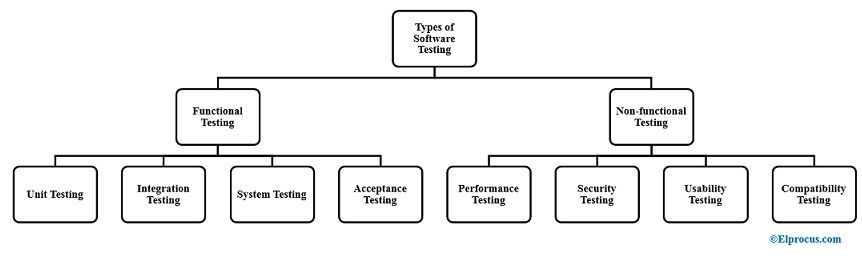

Sequenza di esecuzione delle istruzioni

- IF: recupera l'istruzione nel registro delle istruzioni.

- ID: decodifica istruzione, decodifica l'istruzione per il codice operativo.

- AG: Address Generator, genera l'indirizzo.

- DF: Data Fetch, recupera gli operandi nel registro dati.

- EX: esecuzione, esegue l'operazione specificata.

- WB: riscrive, riscrive il risultato su il registro.

Non tutte le istruzioni richiedono tutti i passaggi precedenti, ma la maggior parte lo fa. Questi passaggi utilizzano diverse funzioni hardware. Nella pipeline queste diverse fasi vengono eseguite contemporaneamente. Nella pipeline queste fasi sono considerate indipendenti tra le diverse operazioni e possono essere sovrapposte. Pertanto, più operazioni possono essere eseguite simultaneamente con ciascuna operazione nella propria fase indipendente.

Pipelining di istruzioni

Esaminiamo il modo in cui le istruzioni vengono elaborate nel pipelining. Questo può essere facilmente compreso dal diagramma sottostante.

Pipelining di istruzioni

Supponiamo che le istruzioni siano indipendenti. Nel semplice pipelining processor, in un dato momento, c'è una sola operazione in ciascuna fase. La fase iniziale è la fase IF. Quindi, al primo ciclo di clock, viene recuperata un'operazione. Quando arriva il successivo impulso di clock, la prima operazione entra nella fase ID lasciando vuota la fase IF. Ora, questa fase vuota viene assegnata all'operazione successiva. Quindi, durante il secondo impulso di clock, la prima operazione è nella fase ID e la seconda operazione è nella fase IF.

Per il terzo ciclo, la prima operazione sarà in fase AG, la seconda operazione sarà in fase ID e la terza operazione sarà in fase IF. In questo modo, le istruzioni vengono eseguite simultaneamente e dopo sei cicli il processore emetterà un'istruzione completamente eseguita per ciclo di clock.

Questa istruzione è stata eseguita in sequenza, inizialmente la prima istruzione deve attraversare tutte le fasi, quindi verrà prelevata l'istruzione successiva? Quindi, per l'esecuzione di ogni istruzione, il processore richiederebbe sei cicli di clock. Ma in un processore in pipeline poiché l'esecuzione delle istruzioni avviene contemporaneamente, solo l'istruzione iniziale richiede sei cicli e tutte le istruzioni rimanenti vengono eseguite come una per ogni ciclo, riducendo così il tempo di esecuzione e aumentando la velocità del processore.

Architettura di pipelining

Il parallelismo può essere ottenuto con tecniche hardware, compilatore e software. Per sfruttare il concetto di pipelining in architettura del computer molte unità processore sono interconnesse e funzionano contemporaneamente. Nell'architettura del processore pipeline, ci sono unità di elaborazione separate fornite per numeri interi e istruzioni in virgola mobile. Mentre nell'architettura sequenziale viene fornita una singola unità funzionale.

Unità processore pipeline

Nella pipeline statica, il processore deve passare l'istruzione attraverso tutte le fasi della pipeline indipendentemente dal requisito dell'istruzione. In un processore a pipeline dinamico, un'istruzione può bypassare le fasi a seconda dei suoi requisiti ma deve spostarsi in ordine sequenziale. In un elaboratore a pipeline dinamico complesso, l'istruzione può bypassare le fasi e scegliere le fasi fuori ordine.

Pipelining nei processori RISC

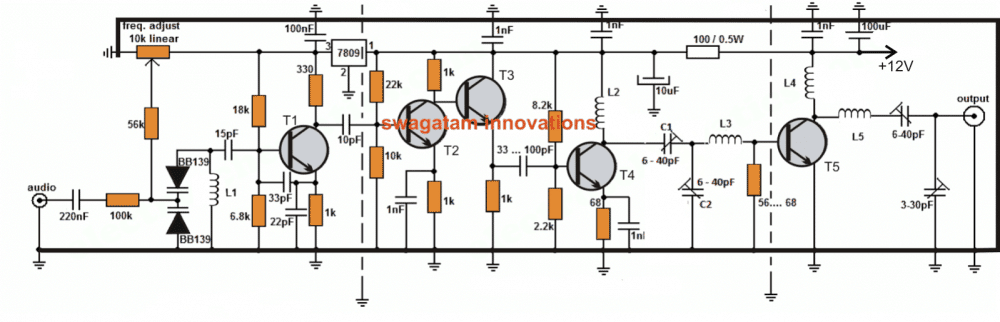

Il più popolare Architettura RISC Il processore ARM segue il pipelining a 3 e 5 fasi. Nella pipeline a 3 fasi le fasi sono: Fetch, Decode ed Execute. Questa pipeline ha una latenza di 3 cicli, poiché una singola istruzione richiede 3 cicli di clock per essere completata.

Pipelining a 3 stadi ARM

Per una corretta implementazione del pipelining, anche l'architettura hardware dovrebbe essere aggiornata. L'hardware per il pipelining a 3 fasi include un banco di registri, ALU, Barrel shifter, generatore di indirizzi, un incrementatore, decodificatore di istruzioni e registri di dati.

Datapath di pipelining a 3 fasi ARM

In 5 fasi di pipeline le fasi sono: Fetch, Decode, Execute, Buffer / data e Write back.

Pericoli di pipelining

In un tipico programma per computer oltre alle semplici istruzioni, ci sono istruzioni di ramo, operazioni di interruzione, istruzioni di lettura e scrittura. Il pipelining non è adatto a tutti i tipi di istruzioni. Quando alcune istruzioni vengono eseguite nella pipeline, possono bloccare la pipeline o scaricarla completamente. Questo tipo di problemi causati durante il pipelining è chiamato Pipelining Hazards.

Nella maggior parte dei programmi per computer, il risultato di un'istruzione viene utilizzato come operando dall'altra istruzione. Quando tali istruzioni vengono eseguite in pipelining, si verifica una scomposizione in quanto il risultato della prima istruzione non è disponibile quando l'istruzione due inizia a raccogliere gli operandi. Quindi, l'istruzione due deve bloccarsi finché l'istruzione uno non viene eseguita e il risultato viene generato. Questo tipo di pericolo è denominato rischio di pipelining di lettura-post-scrittura.

Leggere dopo aver scritto Pipelining Hazard

L'esecuzione delle istruzioni di diramazione causa anche un pericolo di pipelining. Istruzioni di diramazione durante l'esecuzione in pipeline effettua le fasi di recupero delle istruzioni successive.

Comportamento del ramo pipeline

Vantaggi del Pipelining

- Il rendimento delle istruzioni aumenta.

- L'aumento del numero di fasi della pipeline aumenta il numero di istruzioni eseguite simultaneamente.

- Quando si utilizza il pipelining è possibile progettare Faster ALU.

- La CPU pipeline funziona a frequenze di clock più elevate rispetto alla RAM.

- Il pipelining aumenta le prestazioni complessive della CPU.

Svantaggi del Pipelining

- La progettazione del processore pipeline è complessa.

- La latenza delle istruzioni aumenta nei processori pipeline.

- La velocità effettiva di un processore pipeline è difficile da prevedere.

- Più lunga è la pipeline, peggiore è il problema del pericolo per le istruzioni di filiale.

Il pipelining avvantaggia tutte le istruzioni che seguono una sequenza simile di passaggi per l'esecuzione. I processori che hanno istruzioni complesse in cui ogni istruzione si comporta in modo diverso dall'altra sono difficili da pipeline. I processori hanno strumenti ragionevoli con 3 o 5 stadi della pipeline perché all'aumentare della profondità della pipeline aumentano i rischi ad essa correlati. Nominare alcuni dei processori pipeline con la loro fase di pipeline?