L'ECL (emitter coupled logic) è stato inventato per la prima volta all'IBM nell'agosto 1956 da Hannon S. Yourke. Questa logica è anche nota come logica della modalità corrente, utilizzata nei computer di IBM 7090 e 7094. La famiglia ECL è molto veloce rispetto a logica digitale famiglie. In genere, questa famiglia logica prevede un ritardo di propagazione inferiore a 1 ns. È una famiglia logica basata su transistor a giunzione bipolare. È il circuito della famiglia logica più veloce accessibile per la progettazione di un sistema logico convenzionale. Questo articolo discute una panoramica di un circuito logico accoppiato emettitore , lavorando con le applicazioni.

Che cos'è la logica accoppiata all'emettitore?

La logica accoppiata all'emettitore è la migliore BJT famiglia di logica basata su base utilizzata nella progettazione del sistema logico convenzionale. A volte, viene anche chiamata logica della modalità corrente, che è una tecnologia digitale ad altissima velocità. In generale, ECL è considerato il circuito integrato logico più veloce in cui raggiunge il suo funzionamento ad alta velocità utilizzando un'oscillazione di tensione molto piccola ed evitando anche che i transistor entrino nella regione di saturazione.

Un'implementazione di ECL utilizza una tensione di alimentazione positiva nota come PECL o ECL con riferimento positivo. Nelle prime porte ECL, viene utilizzata un'alimentazione di tensione negativa a causa dell'immunità ai disturbi. Successivamente, l'ECL con riferimento positivo è diventato molto famoso grazie ai suoi livelli logici più compatibili rispetto alle famiglie logiche TTL.

La logica accoppiata all'emettitore dissipa un'enorme quantità di potenza statica, tuttavia il suo consumo complessivo di corrente è basso rispetto a CMOS alle alte frequenze. Quindi, l'ECL è principalmente vantaggioso nei circuiti di distribuzione dell'orologio e nelle applicazioni ad alta frequenza.

Caratteristiche della logica accoppiata all'emettitore

Le funzionalità di ECL li renderanno utilizzati in molte applicazioni basate su prestazioni elevate.

- ECL fornisce due uscite che sono sempre complementari l'una all'altra perché il funzionamento del circuito è basato su un amplificatore differenziale.

- Questa famiglia logica è principalmente adatta per metodi di fabbricazione monolitici perché i livelli logici sono una funzione dei rapporti dei resistori.

- I dispositivi della famiglia ECL generano l'uscita giusta e complementare della funzione proposta senza l'utilizzo di inverter esterni. Di conseguenza, diminuisce il conteggio dei pacchetti e i requisiti di alimentazione e riduce anche i problemi che si verificano a causa di ritardi.

- I dispositivi ECL nel design dell'amplificatore differenziale offrono un'ampia flessibilità di prestazioni, quindi i circuiti ECL consentono di essere utilizzati sia come circuiti digitali che lineari.

- Il design del gate ECL ha normalmente un'impedenza di ingresso alta e bassa, che è estremamente favorevole al raggiungimento di un ampio fan-out e della capacità di azionamento.

- I dispositivi ECL generano un consumo di corrente costante sull'alimentatore per semplificare la progettazione dell'alimentatore.

- I dispositivi di ECL che includono uscite di emettitori aperti consentono semplicemente loro di includere la capacità di trasmissione della linea di trasmissione.

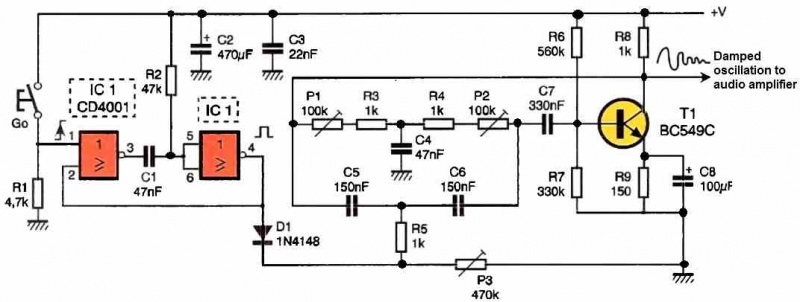

Circuito logico accoppiato all'emettitore

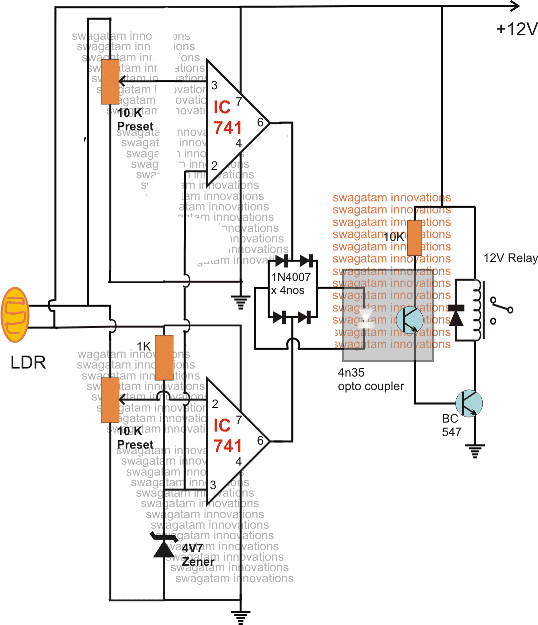

Di seguito è mostrato il circuito logico accoppiato all'emettitore per l'inverter, progettato con resistori e transistor. In questo circuito, i terminali di emettitore di due transistor sono semplicemente collegati alla resistenza di limitazione di corrente RE che viene utilizzata per evitare che il transistor entri in saturazione. Qui l'uscita del transistor viene presa dal terminale di collettore anziché dal terminale di emettitore. Questo circuito fornisce due uscite Vout (uscita invertente) e Vout2 (uscita non invertente) e il terminale di ingresso come Vin dove viene fornito un ingresso alto o basso. +Vcc = 5V.

Come funziona la logica accoppiata all'emettitore?

Il funzionamento della logica accoppiata all'emettitore è che ogni volta che l'ingresso HIGH viene fornito al circuito ECL, il transistor 'Q1' si accende e il transistor Q2 si spegne ma il transistor Q1 non è saturo. Quindi questo porterà l'uscita VOUT2 su ALTO e il valore dell'uscita VOUT1 sarà BASSO a causa della caduta all'interno di R1.

Allo stesso modo, quando il valore VIN assegnato a ECL è BASSO, il transistor Q1 si spegne e il transistor Q2 si accende. Quindi, il transistor Q2 non si sposterà in saturazione. Quindi farà sì che l'uscita VOUT1 venga tirata al valore ALTO e il valore dell'uscita VOUT2 sarà basso a causa della caduta all'interno della resistenza R2.

Vediamo come i transistor Q1 e Q2 si accendono e si spengono quando viene applicata una tensione.

I due transistor come Q1 e Q2 in questo circuito sono collegati come un amplificatore differenziale da un resistore di emettitore comune.

Le alimentazioni di tensione per questo circuito di esempio sono VCC = 5,0, VBB = 4,0 e VEE = 0 V. I valori di livello ALTO e BASSO di ingresso sono semplicemente definiti come 4,4 V e 3,6 V. In realtà, questo circuito genera un'uscita BASSA e livelli ALTI che sono 0,6 Volt più alti; tuttavia, questo viene corretto all'interno di circuiti ECL reali.

Una volta che Vin è ALTO, il transistor Q1 viene acceso, ma non saturo e il transistor Q2 viene spento. Quindi, la tensione di uscita come VOUT2 viene portata a 5 V attraverso il resistore R2 e si può dimostrare che la caduta di tensione attraverso il resistore R1 è di circa 0,8 V in modo che VOUT1 = 4,2 V (LOW). Inoltre VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V poiché il transistor Q1 è completamente acceso.

Una volta che Vin è LOW, il transistor Q2 verrà acceso, ma non saturo e il transistor Q1 verrà spento. Pertanto, VOUT1 viene portato a 5,0 V utilizzando un resistore R1 e si può dimostrare che VOUT2 è 4,2 V. Inoltre VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V quando il transistor Q2 è acceso.

In ECL, i due transistor non sono mai in saturazione come t Le oscillazioni della tensione di ingresso / uscita sono abbastanza piccole come 0,8 v e l'impedenza di ingresso è alta e la resistenza di uscita è bassa. Ciò aiuta l'ECL a funzionare più velocemente con un ritardo di propagazione inferiore.

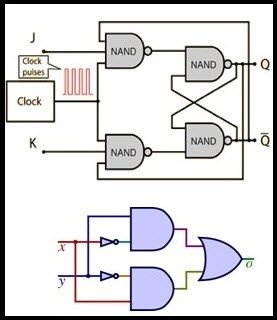

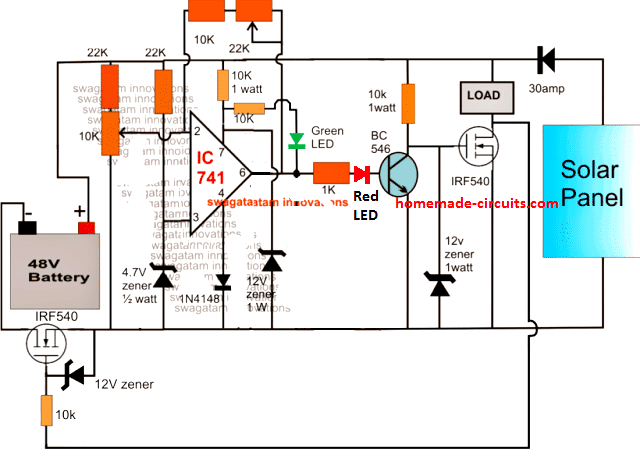

Circuito di gate OR/NOR logico accoppiato con emettitore a due ingressi

Di seguito è mostrato il circuito di gate OR/NOR logico accoppiato con emettitore a due ingressi. Questo circuito è progettato modificando il circuito dell'inverter di cui sopra. La modifica consiste nell'aggiungere un transistor aggiuntivo sul lato di ingresso.

Il funzionamento di questo circuito è molto semplice. Quando gli ingressi applicati a entrambi i transistor Q1 e Q2 sono bassi, l'uscita1 (Vout1) verrà impostata su un valore ALTO. Quindi, questo Vout1corrisponde all'uscita della porta NOR.

Contemporaneamente, se il transistor Q3 è acceso, renderà la seconda uscita (Vout2) ALTA. Quindi, questa uscita Vou2 corrisponde all'uscita del gate OR.

Allo stesso modo, se entrambi gli ingressi dei transistor Q1 e Q2 sono ALTI, accenderà i transistor Q1 e Q2 e fornirà l'uscita bassa al terminale VOUT1.

Se il transistor Q3 viene spento durante questa operazione, fornirà un'uscita elevata al terminale VOUT2. Quindi, la tabella di verità per la porta OR/NOR è riportata di seguito.

|

Ingressi |

Ingressi | O |

NÉ |

|

UN |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Caratteristiche logiche accoppiate all'emettitore

Le caratteristiche di ECL includono quanto segue.

- Rispetto a TTL, ECL ha un tempo di propagazione più veloce che va da 0,5 a 2 ns. Tuttavia, la dissipazione di potenza della logica accoppiata all'emettitore è maggiore rispetto a TTL come 30 mW.

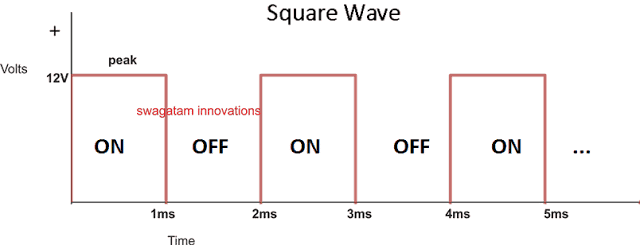

- Le tensioni di I/O di ECL hanno una piccola oscillazione come 0,8.

- L'impedenza di ingresso dell'ECL è alta e la resistenza di uscita è bassa; di conseguenza, il transistor cambia i suoi stati molto velocemente.

- La capacità di fan-out dell'ECL è alta e i ritardi di gate sono bassi.

- La logica o/p di ECL cambia da uno stato BASSO a uno ALTO, ma i livelli di tensione per questi stati varieranno tra TTL ed EC.

- L'immunità al rumore di ECL è 0,4 V.

Vantaggi e svantaggi

Il vantaggi della logica accoppiata all'emettitore sono discussi di seguito.

- Il fanout di ECL è 25, che è migliore rispetto a TTL ed è basso rispetto a CMOS.

- Il tempo medio di ritardo di propagazione di ECL è compreso tra 1 e 4 ns, il che è migliore rispetto a CMOS e

- TTL. Quindi è chiamata famiglia logica più veloce.

- Quando i BJT nell'emettitore si sono accoppiati porte logiche lavorano nella regione attiva, quindi hanno la velocità massima rispetto a tutte le famiglie logiche.

- Le porte ECL generano uscite complementari.

- I picchi di commutazione di corrente non sono presenti nei cavi di alimentazione.

- Le uscite possono essere accoppiate congiuntamente per fornire la funzione OR cablata.

- I parametri di ECL non cambiano molto attraverso la temperatura.

- Il no. di funzioni accessibili da un unico chip è elevato.

Il svantaggi della logica accoppiata all'emettitore sono discussi di seguito.

- Ha un margine di rumore estremamente ridotto, ovvero ±200 mV.

- La dissipazione di potenza è elevata rispetto ad altre porte logiche.

- Per interfacciarsi con altre famiglie logiche, sono necessari i traslatori di livello.

- Il fanout limita il carico capacitivo.

- Paragonato a TTL , i cancelli ECL sono costosi.

- Rispetto a CMOS e TTL, l'immunità al rumore ECL è la peggiore.

Applicazioni

Le applicazioni della logica accoppiata all'emettitore includono quanto segue.

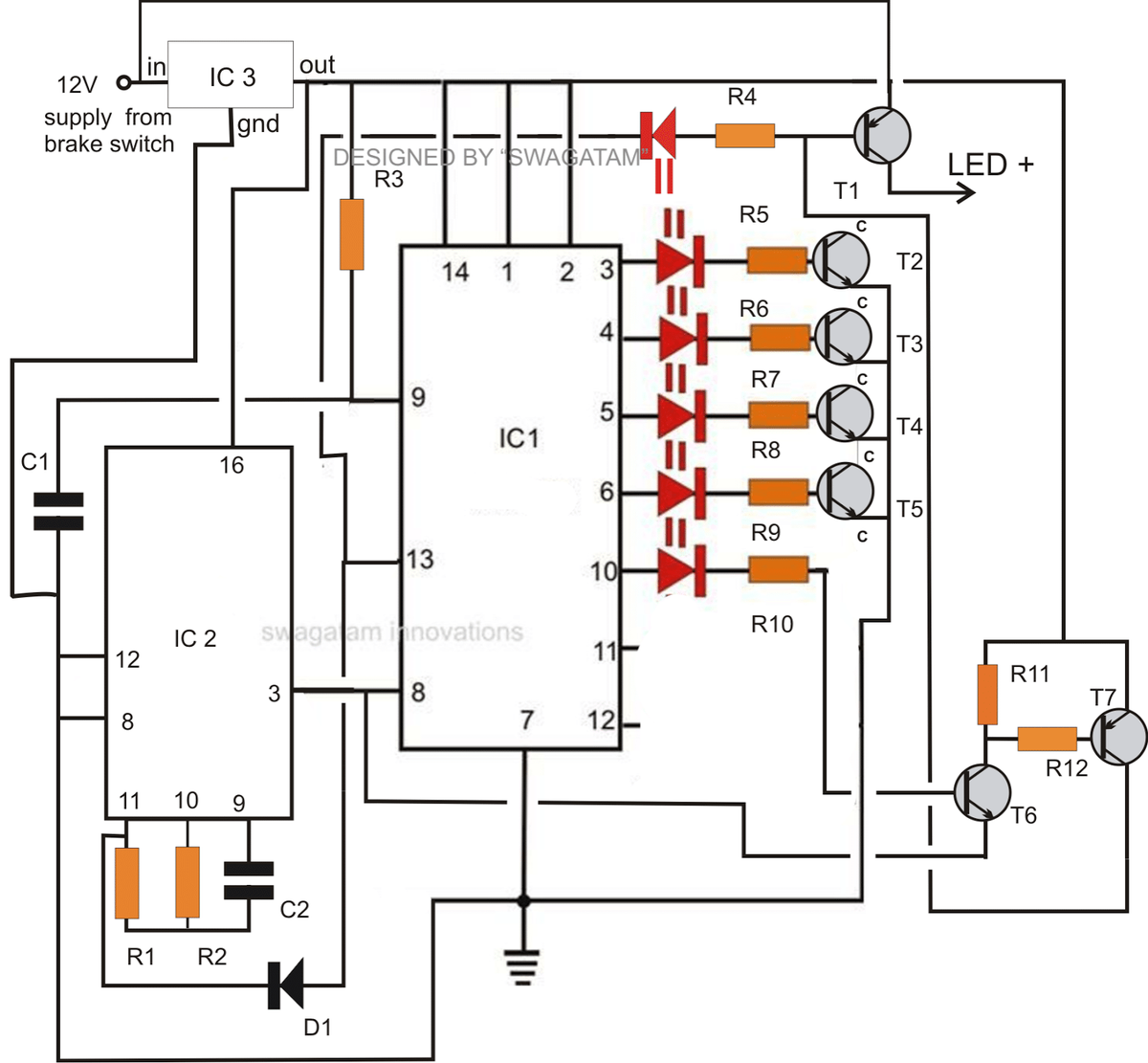

- La logica accoppiata all'emettitore viene utilizzata come tecnologia di interfaccia e logica all'interno di dispositivi di comunicazione ad altissima velocità come interfacce ricetrasmettitori in fibra ottica, reti Ethernet e ATM (modalità di trasferimento asincrono).

- ECL è una famiglia logica basata su BJT in cui il suo funzionamento ad alta velocità può essere ottenuto utilizzando un'oscillazione di tensione relativamente piccola ed evitando che i transistor si spostino nella regione di saturazione.

- ECL viene utilizzato nella realizzazione dei circuiti ASLT all'interno dell'IBM 360/91.

- L'ECL evita l'utilizzo di transistor impilati utilizzando un i/p di polarizzazione single-ended e un feedback positivo tra transistor primari e secondari per ottenere una funzione di inverter.

- L'ECL è utilizzato nell'elettronica ad altissima velocità.

Così, questo è una panoramica di una logica accoppiata all'emettitore o ECL – circuito, funzionamento, caratteristiche, caratteristiche e applicazioni. ECL è una famiglia logica molto più veloce basata su BJT rispetto ad altre famiglie di logica digitale. Raggiunge la sua massima velocità di funzionamento utilizzando una piccola oscillazione di tensione ed evitando che i transistor si spostino nella regione di saturazione. Questa famiglia logica fornisce un incredibile ritardo di propagazione di 1ns e nelle ultime famiglie ECL, questo ritardo è ridotto. Ecco una domanda per te, qual è un nome alternativo per ECL?