Il termine VLSI sta per 'Very Large Scale Integration Technology' che implica la progettazione di circuiti integrati (CI) combinando migliaia di transistor logicamente in un singolo chip da circuiti logici differenti . Questi circuiti integrati alla fine riducono lo spazio del circuito occupato rispetto ai circuiti con circuiti integrati convenzionali. La potenza di calcolo e l'utilizzo dello spazio sono le principali sfide del progetto VLSI. L'implementazione dei progetti VLSI apre una carriera stimolante e brillante per studenti e ricercatori. Alcune delle nuove aree di tendenza di VLSI sono Gate array programmabile sul campo applicazioni (FPGA), progetti ASIC e SOC. Di seguito viene fornito un elenco di alcuni dei progetti VLSI per quegli studenti che cercano seriamente progetti in questo campo. Questo articolo discute una panoramica dei progetti VLSI basati su FPGA, Xilinx, IEEE, Mini, Matlab, ecc. Sono elencati di seguito. Questi progetti sono molto utili per studenti di ingegneria, studenti M.tech.

Progetti VLSI per studenti di ingegneria

I progetti VLSI con abstract per studenti di ingegneria elettronica sono discussi di seguito.

Progetti VLSI

1). Trasformazione di Wavelet discreta basata sul sollevamento 3D

Questo progetto aiuta a fornire immagini altamente precise utilizzando la codifica di un'immagine senza perdere i suoi dati. Per ottenere ciò, questo processo implementa un filtro di sollevamento che dipende dalla trasformazione dell'architettura VLSI wavelet discreta 3D.

2). Progettazione del moltiplicatore SFQ a 4 bit con efficienza tramite hardware ad alta velocità

Questo progetto viene utilizzato principalmente per l'implementazione di un codificatore booth modificato (MBE) con base SFQ a 4 bit moltiplicatore . Questo moltiplicatore fornisce buone prestazioni se confrontato con l'encoder per cabina convenzionale. Questo progetto viene utilizzato principalmente nelle applicazioni di ritardo critico.

3). Processore di crittografia utilizzato nelle smart card con un'area efficiente

Questo progetto viene utilizzato per implementare tre algoritmi di crittografia supportati da chiavi private e pubbliche utilizzate in Smart card applicazioni per fornire dati e verifica utente estremamente sicuri comunicazione .

4). Un moltiplicatore ad alta velocità o bassa potenza con metodo di soppressione della potenza spuria

Questo sistema proposto filtra i falsi segnali inutili delle unità aritmetiche per evitare la trasmissione di dati non necessaria che non influenza gli ultimi risultati di calcolo. Questo sistema utilizza un metodo SPST per moltiplicatori per ottenere una trasmissione dati a bassa potenza e ad alta velocità.

5). Compressione e decompressione di un algoritmo di dati senza perdita di dati

Questo progetto è implementato principalmente per l'architettura hardware a 2 stadi a seconda della funzionalità dell'algoritmo PDLZW (Parallel Dictionary LZW) e dell'algoritmo di tipo Adaptive Huffman che viene utilizzato sia per le applicazioni di compressione dei dati senza perdita che per la decompressione senza perdite.

6). L'architettura del decodificatore turbo a bassa complessità per WSN ad alta efficienza energetica

Il sistema proposto viene utilizzato per ridurre il consumo energetico totale durante la trasmissione dei dati delle WSN attraverso l'algoritmo di decomposizione di LUT-Log-BCJR alle operazioni di base ACS (Add Compare Select).

7). Architettura VLSI per la rimozione efficiente del rumore impulsivo di un'immagine

Questo sistema proposto principalmente utilizzato per migliorare visivamente la qualità dell'immagine per evitare la possibilità di essere corrotti dal rumore impulsivo per implementare un'architettura VLSI efficiente con l'aiuto di un filtro di conservazione dei bordi.

8). L'architettura di un processore in memoria utilizzato per la compressione di contenuti multimediali

Questo sistema proposto fornisce un'architettura a bassa complessità per un file processore in memoria per supportare applicazioni multimediali, ovvero compressione di immagini, video mediante l'applicazione di enormi concetti di singole istruzioni, dati multipli e parole di istruzioni.

9). Tecnica di sincronizzazione temporale con velocità di simbolo per sistemi OFDM wireless a bassa potenza

Questo sistema proposto principalmente utilizzato per migliorare l'azione del wireless OFDM (Orthogonal Frequency Division Multiplexing ) attraverso la diminuzione della potenza dell'intera banda base con l'aiuto di un orologio Generatore con regolatore di temporizzazione del campione sintonizzabile in fase e dinamico.

10). Implementazione del moltiplicatore a bassa potenza e ad alta velocità basata su accumulatori con SPST Adder e Verilog

Questo progetto viene utilizzato per progettare un MAC a bassa potenza e ad alta velocità (moltiplicatore e accumulatore) attraverso l'accettazione del metodo di falsa soppressione dell'alimentazione su un MBE (codificatore cabina modificato). Utilizzando questo design, è possibile evitare la dissipazione di potenza dell'intera commutazione.

11). Progettazione e implementazione del processore robotico abilitando l'anti-collisione con la tecnologia RFID

Il sistema proposto è principalmente utilizzato per implementare un processore robotico con anti-collisione per evitare la collisione fisica dei robot nell'ambiente di multi-robot. Questo algoritmo è implementato principalmente utilizzando la tecnologia VHDL e RFID.

12). Progettazione di circuiti logici con efficienza energetica utilizzando il metodo adiabatico

Questo sistema dimostra la progettazione del circuito logico in modo efficiente con il metodo adiabatico rispetto alla progettazione CMOS convenzionale con l'aiuto di circuiti che utilizzano Porte NAND e NOR . Utilizzando il metodo adiabatico, è possibile ridurre la dissipazione di potenza all'interno della rete e riciclare l'energia immagazzinata all'interno del condensatore di carico.

3). Sistema di crittografia per migliorare la velocità di elaborazione del sistema

L'intenzione principale di questo progetto è migliorare la sicurezza della trasmissione dei dati per migliorare la velocità di elaborazione implementando l'algoritmo di AES utilizzando FPGA. Quindi, questa simulazione, così come la progettazione matematica, può essere eseguita con l'aiuto del codice VHDL.

14). Blocco IP di AHM o Advanced High-Performance Bus

Questo progetto è utilizzato principalmente per progettare un'architettura dell'Advanced Microcontrollore Bus (AMB) utilizzando AHBN (Advanced High-Performance Bus). Questo progetto può essere progettato con codice VHDL implementando i blocchi come master & save.

15). Ricetrasmettitore RF multimodale basato su DSM con multicanale

Questo sistema è utilizzato principalmente per progettare un'architettura di trasmettitore e ricevitore multimodale e multicanale RF con modulatore Delta-Sigma. Questo sistema proposto utilizza un linguaggio VHDL per implementare due architetture.

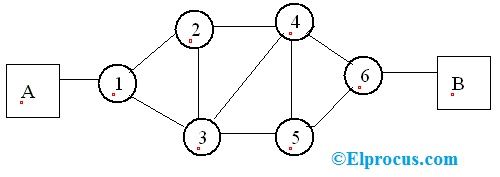

16). Il concentratore di Knockout Switch che utilizza una modalità di trasferimento asincrono

Utilizzando questo progetto, è possibile progettare un interruttore knockout basato sul trasferimento asincrono con l'aiuto di strumenti come VHS e VHDL. Questo interruttore knock out può essere utilizzato nelle reti di pacchetti di circuiti virtuali così come nelle applicazioni del datagramma.

17). Sintesi comportamentale dei circuiti asincroni

Questo progetto viene utilizzato principalmente per fornire la tecnica di sintesi comportamentale utilizzata per i circuiti asincroni. Entrambi i modelli come la balsa e le implementazioni asincrone sono gli elementi principali all'interno del design.

18). Progettazione AMBA utilizzando il controller di memoria conforme di AHB

Questo progetto viene utilizzato per progettare un MC (controller di memoria) dipendente da AMBA (Advanced Microcontroller Bus Architecture) per il controllo della memoria di sistema utilizzando la memoria principale come SRAM e ROM.

19). Carry Tree Adder implementazione

I sommatori di alberi portanti basati sul design VLSI sono chiamati i migliori sommatori di prestazioni in contrasto con i soliti sommatori binari. Le sommità che sono implementate da questo progetto sono spanning tree, kogge-stone e sparse kogge-stone.

20). Rotazione dell'angolo fisso basata sul design CORDIC

Il concetto principale di questo sistema proposto è trasformare i vettori usando angoli fissi. Questi angoli sono necessari per giochi, robotica, elaborazione delle immagini , ecc. Utilizzando questo progetto, la rotazione vettoriale può essere ottenuta utilizzando angoli specifici secondo la progettazione di CORDIC (computer digitale di rotazione delle coordinate).

21). Progettazione di filtri FIR con aritmetica distribuita della tabella di ricerca

Questo sistema proposto migliora principalmente Filtro FIR prestazioni progettandola utilizzando l'aritmetica distribuita di una tabella di ricerca tridimensionale al posto del moltiplicatore. Quindi questo design può essere implementato utilizzando software come FPGA e Xilinx.

22). Chiusure push-pull pulsate con condizioni ad alta velocità e bassa potenza

Questo progetto viene utilizzato per eseguire latch pulsati ad alta efficienza energetica e ad alte prestazioni utilizzati principalmente per i sistemi VLSI utilizzando una nuova topologia. Perché questa topologia dipende principalmente da uno stadio finale push-pull pilotato utilizzando due corsie di divisione attraverso un generatore di impulsi condizionato.

23). Architettura VLSI del codificatore aritmetico in SPIHT

Questo sistema proposto migliora il throughput del metodo di codifica aritmetica nella compressione delle immagini del partizionamento di set in alberi gerarchici (SPIHT) con l'architettura ad alta velocità dipendente dall'FPGA.

24). Soppressione del rumore del segnale ECG basata su FPGA

Questo progetto viene utilizzato per contenere il rumore all'interno dei segnali ECG attraverso due filtri mediani con rispettivamente 91 e 7 dimensioni dei punti di campionamento. Quindi questo processo può essere ottenuto implementando il Progettazione FPGA basato sul codice VHDL.

25). Processore di ridimensionamento delle immagini ad alte prestazioni basato su VLSI a basso costo

Questo progetto viene utilizzato per implementare un algoritmo per il processore di ridimensionamento delle immagini basato su VLSI con meno memoria e prestazioni elevate. Il progetto di sistema proposto contiene principalmente la combinazione di filtri, metodi dinamici riconfigurabili e condivisione dell'hardware per ridurre i costi.

26). Progettazione e implementazione dell'architettura di array sistolici in modo efficiente

Il concetto principale di questo progetto è progettare un modello hardware utilizzato per il moltiplicatore di array sistolico. Questo array può essere utilizzato principalmente per eseguire la moltiplicazione binaria con l'aiuto della piattaforma VHDL. Il progetto di sistema proposto può essere implementato utilizzando software FPGA e Isim.

27). Progettazione e sintesi QPSK utilizzando il codice VHDL

QPSK è uno dei principali metodi di modulazione. Questo metodo è utilizzato nelle applicazioni della radio satellitare. Questa tecnica di modulazione può essere implementata tramite porte logiche reversibili. La progettazione della tecnica QPSK può essere eseguita con l'aiuto del codice VHDL.

28). Progettazione e implementazione di controller DDR SDRAM ad alta velocità

Il sistema proposto viene utilizzato per progettare un controller DDR SDRAM per il trasferimento dei dati burst in base all'alta velocità per sincronizzare questi dati tra i circuiti del sistema embedded e DDR SDRAM. Utilizzando il linguaggio VHDL, il codice può essere sviluppato.

29). Progettazione e implementazione del processore RISC a 32 bit

Il concetto principale di questo progetto è implementare un 32 bit RISC (Computer con set di istruzioni ridotto) con l'aiuto di uno strumento come XILINK VIRTEX4. In questo progetto, vengono progettati 16 set di istruzioni ovunque ogni istruzione possa essere eseguita in un singolo ciclo CLK utilizzando il metodo di pipelining a cinque fasi.

30). Implementazione di bus bridge tra AHB e OCP

Il sistema proposto viene utilizzato per progettare un bus bridge tra due protocolli, vale a dire comune e standard. I protocolli di comunicazione come AHB (Advanced High-performance Bus) e OCP (Open Core Protocol) sono molto popolari che vengono utilizzati nelle applicazioni di SoC (sistema su chip) .

Idee per progetti VLSI per studenti di ingegneria

Di seguito è riportato l'elenco dei progetti VLSI basati su FPGA, MatLab, IEEE e Mini progetti per studenti di ingegneria.

Progetti VLSI per studenti M. Tech

L'elenco dei progetti VLSI basati su M. Tech Students include quanto segue.

- Design delle celle di memoria I0T basato su RHBD efficiente e altamente affidabile utilizzato nelle applicazioni aerospaziali

- Rilevatore di fase con Half-Rate multilivello utilizzato per CLK e circuiti di recupero dati

- Comparatore a bassa potenza e alta velocità utilizzato per applicazioni precise

- Traduttore del livello di tensione con gate con multiplexer integrato e ad alte prestazioni

- Sommatore ternario basato su CNTFET ad alte prestazioni

- Design del comparatore di magnitudo a bassa potenza

- Progettazione del gate logico di soglia con modalità di corrente per l'analisi del ritardo

- Decodificatori di linea a logica mista progettati a bassa potenza e ad alte prestazioni

- Progettazione della testabilità della logica della convenzione del sonno

- Cambio del livello di tensione per applicazioni a doppia alimentazione ad alta velocità ed efficienza energetica

- Progettazione e analisi di comparatori a doppia coda a bassa potenza e bassa tensione

- Design flip-flop basato su trigger a impulsi con bassa potenza utilizzando un metodo di trasmissione del segnale

- Progettazione di circuiti efficienti basata su FET riconfigurabili a runtime

- Design del comparatore di magnitudo a bassa potenza

- Analisi del ritardo dei progetti di porte logiche con soglia in modalità corrente

Il Progetti VLSI basati su FPGA per studenti di ingegneria e CMOS VLSI progetta mini-progetti sono elencati di seguito.

- SEU Hardened Circuits Design & Characterization per FPGA basato su SRAM

- Un design LUT ibrido CMOS basato su Memristor compatto e potenziale applicazione utilizzata in FPGA

- Implementazione basata su sensori a ultrasuoni di FPGA per la misurazione della distanza

- Implementazione di FPGA per Booth Multiplier con FPGA Spartan6

- Trasformazione Wavelet discreta basata sul sollevamento con FPGA Spartan3

- Controller ARM in Robotica utilizzando FPGA

- UART basato su FPGA con multicanale

- Soppressione del rumore del segnale ECG mediante FPGA

- Implementazione FPGA basata su UTMI e livello di protocollo USB 2.0

- Implementazione del filtro mediano con FPGA Spartan3

- Implementazione basata su algoritmo AES di FPGA

- Security Alert System basato su PIC per l'implementazione di FPGA con Spartan 3an

- Implementazione FPGA per progettare il controller per sistemi di telerilevamento

- Image Processing Kit di FPGA utilizzando Image Filtering di Linear & Morphological

- Implementazione dell'immagine Medical Fusion basata su FPGA Spartan3

L'elenco di Mini progetti VLSI che utilizzano codice VHDL include quanto segue.

- Comparatore con alta velocità utilizzando VLSI

- Un moltiplicatore di virgola mobile utilizzando VLSI

- Conversione basata su VLSI di binario in grigio

- Filtro digitale

- Gating CLK basato su VLSI

- Moltiplicatore vedico

- CMOS FF utilizzando VLSI

- L'architettura di Parallel Processor utilizzando VLSI

- Sommatore completo basato su VLSI

- Progettazione di DRAM / memoria dinamica ad accesso casuale basato su VLSI

- Layout SRAM basato su VLSI

- Processore di segnale digitale basato su VLSI

- Multiplexer basato su VLSI

- Progettazione di MAC Unit basata su VLSI

- Differenziatore basato su VLSI

- FFT o trasformata veloce di Fourier basata su VLSI

- L'architettura di Discrete Cosine Transform basata su VLSI

- Moltiplicatore a 16 bit Design utilizzando VLSI19

- Progettazione basata su VLSI di buffer FIFO

- Acceleratore ad alta velocità basato su VLSI

Progetti VLSI che utilizzano MATLAB e Xilinx

L'elenco dei progetti VLSI basati su MATLAB e progetti VLSI che utilizzano Xilinx include quanto segue.

- Progettazione e analisi del modem CDMA con MATLAB

- Progettazione di filtri FIR utilizzando VHDL su FPGA e analisi basata su MATLAB

- Simulazione del sistema basata su ModelSim e Matlab o Simulink per l'ingegneria automobilistica

- Adder basati su Xilinx come Ripple Carry & Carry Skip

- Unità aritmetica basata su virgola mobile a 32 bit

- ALU a virgola mobile

- Processore RISC basato su 32 bit

- Capacità di convoluzione del codice ortogonale

- Distributore automatico basato su Xilinx e Verilog

- Sommatori di prefissi paralleli basati su Xilinx con 256 bit

- Protocollo per l'autenticazione reciproca utilizzando Xilinx

- Struttura di accesso con ciclo singolo per test logici utilizzando Xilinx

- UTMI e protocollo USB 2.0 basato su livello utilizzando Xilinx

- Configurazione della compressione e decompressione dei dati utilizzando Xilinx FPGA

- FPGA basati su Xilinx 4000 basati su BIST e su serie Spartan

- Filtro IIR basato su MATLAB e VLSI

- Filtro FIR utilizzando MATLAB

Progetti IEEE

Il elenco dei progetti IEEE VLSI è elencato di seguito.

- Sistema di automazione domestica wireless basato su VLSI tramite Bluetooth

- Rimozione del rumore degli impulsi all'interno dell'immagine utilizzando un'architettura efficiente di VLSI

- L'architettura di un processore in memoria per la compressione multimediale

- Monitoraggio del sistema di temperatura utilizzando Cloud e IoT

- Implementazione del sistema OFDM con IFFT e FFT

- Progettazione e implementazione del codice Hamming con Verilog

- Riconoscimento dell'impronta digitale basato su VHDL utilizzando il filtro Gabor

- Rimappatura di funzioni aritmetiche con ROM in base agli approcci di approssimazione

- Analisi delle prestazioni ad alta efficienza e bassa densità del decodificatore di codice con controllo di parità in applicazioni a bassa potenza

- Architetture FFT con feedforward di Pipelined Radix-2k

- Design flip-flop per applicazioni VLSI utilizzando la tecnologia CMOS ad alte prestazioni

- Progettazione di filtri FIR con tabella di ricerca per aritmetica distribuita

- Processore di ridimensionamento delle immagini a basso costo e avanzato basato su VLSI

- Implementazione e progettazione ASIC di un codificatore e decodificatore turbo avanzato con 3GPP LTE

- Chiusure push-pull pulsate con condizioni di bassa potenza e alta velocità

- Scansione avanzata nel test di scansione a bassa potenza

- Architettura VLSI del codificatore aritmetico per SPIHT

- Implementazione di VHDL per UART

- Regolatore di tensione basato su VLSI con bassa caduta di tensione

- Progettazione Flash ADC con schema di confronto avanzato

- Design del moltiplicatore a bassa potenza con stile logico a ritardo costante composto

- Comparatore a doppia coda con alte prestazioni e bassa potenza

- Sistema di archiviazione flash con prestazioni elevate a seconda del buffer di scrittura e della memoria virtuale

- FF a bassa potenza basato sull'approccio Sleepy Stack

- Ottimizzazione della potenza LFSR per BIST a bassa potenza implementata in HDL

- Progettazione e implementazione di distributori automatici con Verilog HDL

- Design dell'accumulatore basato sulla generazione del modello a 3 pesi con LP-LSFR

- Decoder Reed-Solomon ad alta velocità e bassa complessità

- Tecnica di progettazione del moltiplicatore Dadda più veloce

- Ricevitore basato su demodulazione digitale della radio FM

- Generazione di test pattern con schemi BIST

- Implementazione dell'architettura VLSI con pipeline ad alta velocità

- Progettazione del protocollo OCP su chip bus utilizzando le funzionalità del bus

- Rilevatore di frequenza di fase e design della pompa di carica utilizzati per loop ad alta frequenza con blocco di fase

- Memoria cache e progettazione di controller cache con VHDL

- Implementazione basata su ASTRAN di compressori sommatori 3-2 e 4-2 a bassa potenza

- Sistema di fatturazione prepagato dell'elettricità utilizzando un design su chip

- Implementazione di sovrapposizione utilizzando la cella logica e la sua analisi di potenza

- Porta lo sguardo avanti Adder con diversa analisi delle prestazioni in bit utilizzando VHDL

- Data Link Layer Design con Wi-Fi MAC Protocolli

- Implementazione di FPGA per protocollo di mutua autenticazione con aritmetica modulare

- Generazione del segnale PWM utilizzando FPGA e ciclo di lavoro variabile

Progetti in tempo reale

L'elenco di Progetti VLSI in tempo reale includono principalmente mini progetti VLSI che utilizzano codice VHDL e progetti software VLSI per studenti di ingegneria ECE.

- Integrazione pragmatica della cache di riga SRAM in un'architettura DRAM 3-D eterogenea mediante TSV

- Tecnica di autoverifica integrata per la diagnosi di guasti di ritardo in matrici di gate programmabili sul campo basate su cluster

- Progettazione ASIC di moltiplicatori complessi

- Un'implementazione VLSI a basso costo per una rimozione efficiente del rumore impulsivo

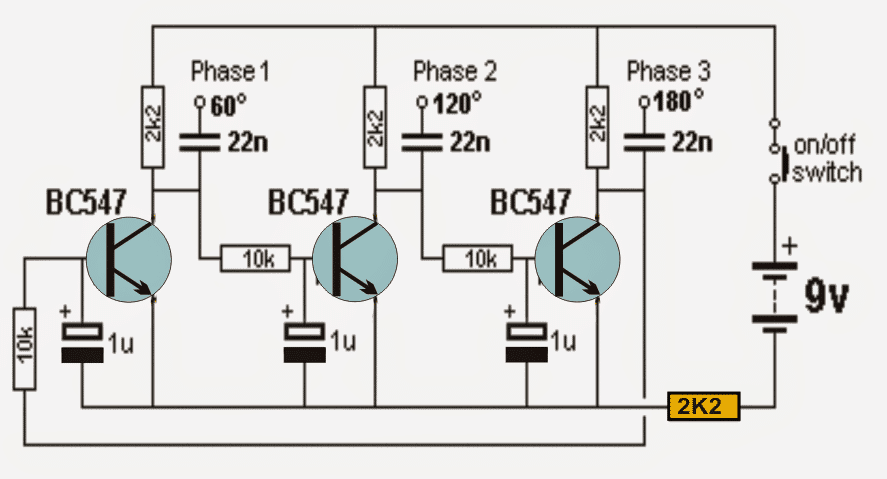

- Basato su FPGA Space Vector PWM CI di controllo per azionamento con motore a induzione trifase

- Implementazione VLSI di Auto Correlator e algoritmo CORDIC per WLAN basata su OFDM

- Estrazione automatica della strada mediante immagini satellitari ad alta risoluzione

- Progettazione VHDL per la segmentazione delle immagini utilizzando il filtro Gabor per il rilevamento delle malattie

- Un'architettura del decodificatore turbo a bassa complessità per reti di sensori wireless ad alta efficienza energetica

- Miglioramento delle capacità di convoluzione del codice ortogonale utilizzando l'implementazione FPGA

- Progettazione e realizzazione di Floating Point ALU

- Design CORDICO per angolo di rotazione fisso

- Codici Reed-Solomon del prodotto per l'implementazione del controller flash NAND su chip FPGA

- Miglioramento della resa di accesso in lettura statistica SRAM utilizzando circuiti di capacità negativa

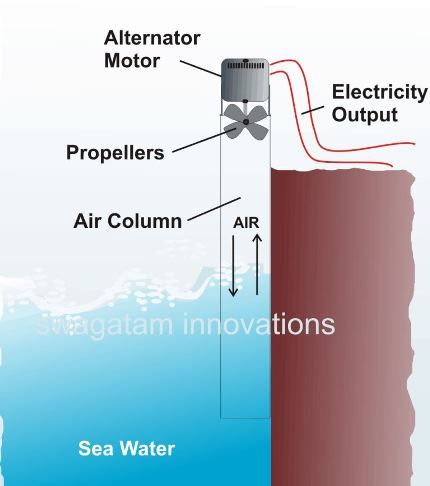

- Gestione energetica delle interfacce di rete MIMO su sistemi mobili

- Progettazione dello standard di crittografia dei dati per la crittografia dei dati

- Adder Select per il trasporto a bassa potenza ed efficiente in area

- Sintesi e implementazione di UART utilizzando codici VHDL

- Architetture migliorate per un'unità di addizione e sottrazione a virgola mobile fusa

- Un trasmettitore completamente digitale a 1 bit basato su FPGA che utilizza la modulazione Delta-Sigma con uscita RF per SDR

- Ottimizzazione dell'utilizzo della ricerca a catena nel decodificatore BCH per la trasmissione ad alto tasso di errore

- Progettazione digitale del trasmettitore DS-CDMA con Verilog HDL e FPGA

- Progettazione e implementazione di un'architettura di array sistolica efficiente

- Un algoritmo di apprendimento della dinamica dei robot basato su VLSI

- Un design versatile dell'unità funzionale multimediale che utilizza la tecnica di soppressione dell'alimentazione spuria

- Progettazione di Bus Bridge tra AHB e OCP

- Sintesi comportamentale di circuiti asincroni

- Ottimizzazione della velocità di un decodificatore Viterbi modificato basato su FPGA

- Implementazione dell'interfaccia I2C

- Un moltiplicatore ad alta velocità / bassa potenza che utilizza una tecnica avanzata di soppressione della potenza spuria

- Bloccaggio della tensione di alimentazione virtuale dei circuiti con gate di alimentazione per la riduzione attiva delle perdite e l'affidabilità dell'ossido di gate

- Channelizer efficiente dal punto di vista energetico basato su FPGA per Software Defined Radio

- Architettura VLSI e prototipazione FPGA di una fotocamera digitale per la sicurezza e l'autenticazione delle immagini

- Miglioramento del funzionamento del robot da interni

- Progettazione e implementazione di una rete di permutazione ON-Chip per multiprocessore System-On-Chip

- Un metodo di sincronizzazione dei tempi a velocità di simbolo per sistemi OFDM wireless a bassa potenza

- Controller DMA (accesso diretto alla memoria) utilizzando VHDL / VLSI

- FFT riconfigurabile utilizzando l'architettura basata su CORDIC per ricevitori MIMI-OFDM

- Tecnica di soppressione dell'alimentazione spuria per applicazioni multimediali / DSP

- L'efficienza dei codici BCH nella filigrana di immagini digitali

- Controller SD-RAM a doppia velocità di trasmissione dati

- Implementazione del filtro Gabor per il riconoscimento delle impronte digitali utilizzando Verilog HDL

- Progettazione di una pratica scala nanometrica ridondante tramite libreria di celle standard consapevole per una ridondanza migliorata tramite 1 velocità di inserimento

- Un algoritmo di compressione e decompressione dei dati senza perdite e la sua architettura hardware

- Un framework per la correzione di errori soft multi-bit

- Compressione dei dati di prova efficiente basata su Viterbi

- Implementazione di blocchi FFT / IFFT per OFDM

- Compressione di immagini basata su Wavelet mediante codifica progressiva VLSI

- Implementazione VLSI di un moltiplicatore completamente a pipeline senza architettura 2d DCT / IDCT per Jpeg

- Emulazione dei guasti basata su FPGA di circuiti sequenziali sincroni

Quindi, questo riguarda l'elenco dei progetti VLSI per l'ingegneria, studenti M.Tech che sono utili nella selezione dell'argomento del progetto dell'ultimo anno. Dopo aver speso il tuo tempo prezioso esaminando questo elenco, riteniamo che tu abbia una buona idea di selezionare l'argomento del progetto di tua scelta dall'elenco dei progetti VLSI e speriamo che tu abbia abbastanza fiducia per affrontare qualsiasi argomento dal elenco. Per ulteriori dettagli e aiuto con questi progetti, puoi scriverci nella sezione commenti riportata di seguito. Ecco una domanda per te, cos'è VHDL?

Diritti d'autore della foto

- Progetti VLSI di set-tech