JTAG (Joint Test Action Group) è uno standard IEEE 1149.1 consolidato che è stato sviluppato nell'anno 1980 per risolvere i problemi di produzione che si verificavano all'interno di schede elettroniche o circuiti stampati . Questa tecnologia viene utilizzata per fornire un accesso di prova sufficiente per ciascuna scheda complessa quando l'accesso di prova stava diminuendo. Pertanto, è stata lanciata la tecnologia di scansione dei confini e lo standard JTAG o Specifica JTAG è stabilito. La complessità dell'elettronica è aumentata di giorno in giorno, quindi la specifica JTAG è diventata il formato di prova accettato per testare unità elettroniche complicate e compatte. Questo articolo discute una panoramica di a JTAG protocollo: lavorare con le applicazioni.

Cos'è JTAG?

Il nome assegnato alla porta di accesso ai test standard IEEE 1149.1 e all'architettura Boundary-Scan è noto come JTAG (Joint Test Action Group). Questa architettura di scansione dei confini viene utilizzata principalmente all'interno del computer processori perché il primo processore con JTAG è stato rilasciato da Intel. Questo standard IEEE definisce semplicemente come viene testato il circuito di un computer per confermare se funziona correttamente dopo la procedura di produzione. Sulle schede elettroniche vengono eseguiti dei test per verificare i giunti di saldatura.

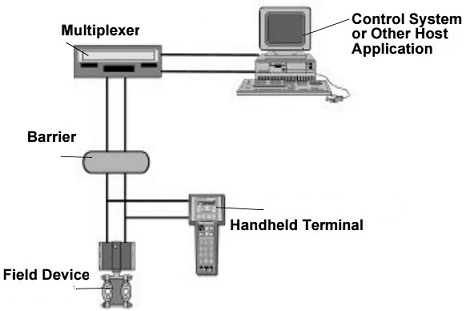

Il Joint Test Action Group fornisce una vista dettagliata per i tester con ogni pad IC che aiuta a identificare eventuali guasti all'interno di una scheda a circuito. Una volta che questo protocollo è interfacciato a un chip, questo può collegare una sonda al chip consentendo a uno sviluppatore di controllare il chip e le sue connessioni con altri chip. L'interfaccia con il gruppo Joint Test Action può essere utilizzata anche dagli Sviluppatori per copiare il firmware su memoria non volatile in un dispositivo elettronico.

Configurazione/Pin Out

Il Joint Test Action Group comprende 20 pin in cui ogni pin e la sua funzione sono discussi di seguito.

Pin1 (VTref): Questo è il pin della tensione di riferimento del target utilizzato per il collegamento all'alimentazione principale del target che varia da 1,5 a 5,0 V CC.

Pin2 (Valimentazione): Questa è la tensione di alimentazione target utilizzata per collegare l'alimentazione di tensione principale di target 1,5 V CC – 5,0 V CC.

Pin3 (nTRST): Questo è un pin di ripristino del test che viene utilizzato per ripristinare la macchina a stati del controller TAP.

Pin (4, 6, 8, 10, 12, 14, 16, 18 e 20): Questi sono pin GND comuni.

Pin5 (TDI): Questi sono i dati di prova nel pin. Questi dati vengono trasferiti nel dispositivo di destinazione. Questo pin deve essere sollevato in una condizione definita sulla scheda target.

Pin7 (TMS): Questo è il pin Test Mode State che viene estratto per determinare la condizione successiva della macchina a stati del controller TAP.

Pin9 (TCK): Questo è un pin di test clock che sincronizza le operazioni interne della macchina a stati nel controller TAP.

Pin11 (RTCK): Questo è il pin Input Return TCK utilizzato nei dispositivi che supportano il clock adattivo.

Pin13 (TDO): Questo è il pin Test Data Out, quindi i dati vengono spostati dal dispositivo di destinazione nel Flyswatter.

Pin15 (nSRST): Questo è il pin Target System Reset che è collegato al segnale di reset principale del target.

Pin 17 e 19 (NC): Questi non sono pin collegati.

JTAG funzionante

L'uso originale del JTAG è per i test di confine. Ecco un semplice circuito stampato che include due circuiti integrati come CPU e FPGA . Una scheda tipica può includere molti circuiti integrati. In generale, i circuiti integrati includono molti pin che sono collegati insieme a molte connessioni. Qui, nel diagramma seguente, sono mostrate solo quattro connessioni.

Quindi, se progetti molte schede in cui ogni scheda ha migliaia di connessioni. In questo, ci sono alcune schede difettose. Quindi dobbiamo controllare quale scheda funziona e quale non funziona. Per questo è stato progettato il Joint Test Action Group.

Questo protocollo può utilizzare i pin di controllo di tutti i chip, ma nel diagramma seguente, il Joint Test Action Group realizzerà tutti i pin di uscita della CPU e tutti i pin di ingresso dell'FPGA. Dopodiché, trasmettendo una certa quantità di dati dai pin della CPU e leggendo i valori dei pin dall'FPGA, JTAG afferma che i collegamenti della scheda PCB sono a posto.

In realtà, il Joint Test Action Group comprende quattro segnali logici TDI, TDO, TMS e TCK. E questi segnali devono essere collegati in un modo particolare. Inizialmente, TMS e TCK sono collegati in parallelo a tutti i circuiti integrati di JTAG.

Successivamente, sia il TDI che il TDO sono collegati per formare una catena. Come puoi osservare, ogni IC conforme a JTAG include 4 pin che vengono utilizzati per JTAG dove 3 pin sono ingressi e 4 pin viene emesso. Il quinto pin come TRST è opzionale. Di solito, i pin JTAG non vengono condivisi per altri scopi.

Utilizzando il Joint Test Action Group, tutti gli IC utilizzano i test di confine il cui motivo originale è stato creato da JTAG. Al momento, l'uso di questo protocollo è stato esteso per consentire diverse cose come la configurazione di FPGA e successivamente JTAG viene utilizzato nel core FPGA per scopi di debug.

Architettura JTAG

L'architettura JTAG è mostrata di seguito. In questa architettura, tutti i segnali tra la logica centrale del dispositivo e i pin vengono interrotti attraverso un percorso di scansione seriale chiamato BSR o Boundary Scan Register. Questo BSR include varie 'celle' di scansione dei confini. In genere, queste celle di scansione dei confini non sono visibili, ma possono essere utilizzate per impostare o leggere valori in modalità test dai pin del dispositivo.

L'interfaccia JTAG chiamata TAP o Test Access Port utilizza segnali diversi per supportare l'operazione di scansione dei confini come TCK, TMS, TDI, TDO e TRST.

- Il segnale TCK o Test Clock sincronizza semplicemente le operazioni interne di una macchina a stati.

- Il segnale TMS o Test Mode Select viene campionato sul fronte crescente di un segnale di clock di prova per decidere lo stato successivo.

- Il segnale TDI o Test Data In indica i dati spostati nel dispositivo di test, altrimenti la logica di programmazione. Una volta che la macchina a stati interni è nello stato corretto, viene campionata sul fronte crescente di TCK.

- Il segnale TDO o Test Data Out indica i dati spostati fuori dal dispositivo di test, altrimenti la logica di programmazione. Una volta che la macchina a stati interni è nello stato corretto, è valida sul fronte decrescente di TCK

- TRST o Test Reset è un pin opzionale utilizzato per ripristinare la macchina a stati del controller TAP.

Controllore TAP

Il punto di accesso al test nell'architettura di JTAG è composto da un controller TAP, un registro delle istruzioni e registri dei dati del test. Questo controller include la macchina a stati di test che è responsabile della lettura dei segnali TMS e TCK. Qui, il pin data i/p viene semplicemente utilizzato per caricare i dati nelle celle di confine tra il core IC e i pin fisici, e anche caricare i dati in uno dei registri dati o nel registro delle istruzioni. Il pin data o/p viene utilizzato per leggere i dati dai registri o dalle celle limite.

La macchina a stati del controller TAP è controllata dal TMS ed è sincronizzata da TCK. La macchina a stati utilizza due percorsi per indicare due diverse modalità come la modalità istruzione e la modalità dati.

Registri

Ci sono due tipi di registri disponibili all'interno della scansione dei confini. Ogni dispositivo conforme include minimo due o più registri di dati e un registro di istruzioni.

Registro delle istruzioni

Il registro delle istruzioni viene utilizzato per contenere l'istruzione corrente. Quindi i suoi dati vengono utilizzati dal controller TAP per decidere cosa eseguire con i segnali ottenuti. Nella maggior parte dei casi, i dati del registro di istruzioni descrivono a quale dei registri di dati devono essere trasmessi i segnali.

Registri di dati

I registri dei dati sono disponibili in tre tipi: il registro BSR (Boundary Scan Register), il BYPASS e il registro ID CODES. Inoltre, potrebbero essere presenti altri registri di dati, tuttavia non sono necessari come elemento dello standard JTAG.

Registro di scansione del confine (BSR)

BSR è il registro dei dati di test principale utilizzato per spostare i dati da e verso i pin I/O del dispositivo.

CIRCONVALLAZIONE

Bypass è un registro a bit singolo utilizzato per trasferire dati da TDI – TDO. Quindi consente di testare dispositivi aggiuntivi all'interno di un circuito con un sovraccarico minimo.

CODICI ID

Questo tipo di registro dati include il codice ID e il numero di revisione del dispositivo. Quindi questi dati consentono al dispositivo di essere collegato al suo file BSDL (Boundary Scan Description Language). Questo file includeva i dettagli di configurazione di Boundary Scan per il dispositivo.

Il funzionamento di JTAG è, inizialmente, la modalità di istruzione viene scelta in cui uno degli stati in questa modalità 'percorso' consente all'operatore di cronometrare all'interno di un'istruzione di TDI. Dopodiché, la macchina a stati si sviluppa finché non si riorganizza. Il passaggio successivo per la maggior parte delle istruzioni è scegliere la modalità dati. Quindi in questa modalità, i dati vengono caricati tramite TDI per essere letti da TDO. Per TDI e TDO, i percorsi dei dati saranno organizzati in conformità con l'istruzione che è stata sincronizzata. Una volta eseguita l'operazione di lettura/scrittura, la macchina a stati passa nuovamente allo stato di ripristino.

Differenza tra JTAG e UART

La differenza tra JTAG e UART include quanto segue.

| JTAG |

UART |

| Il termine 'JTAG' sta per Joint Test Action Group. | Il termine ' UART ” sta per ricevitore/trasmettitore asincrono universale. |

| È un'interfaccia sincrona che utilizza hardware integrato per la programmazione del flash . | UART è un'interfaccia asincrona che utilizza un bootloader che viene eseguito in memoria. |

| È un insieme di porte di test che vengono utilizzate per il debug ma possono anche essere utilizzate per programmare il firmware (cosa che viene comunemente eseguita).

|

UART è un tipo di chip che controlla le comunicazioni da e verso un dispositivo, come un microcontrollore, ROM, RAM, ecc. Il più delle volte è una connessione seriale che ci consente di comunicare con un dispositivo. |

| Questi sono disponibili in quattro tipi TDI, TDO, TCK, TMS e TRST. | Questi sono disponibili in due tipi muti UART e FIFO UART. |

| Il Joint Test Action Group è un protocollo di programmazione seriale o di accesso ai dati utilizzato nell'interfacciamento di microcontrollori e dispositivi correlati. | Un UART è un tipo di chip altrimenti sottocomponente del microcontrollore che viene utilizzato per fornire l'hardware per generare un flusso seriale asincrono come RS-232/RS-485. |

| I componenti JTAG sono Processori, FPGA, CPLD , eccetera. | I componenti UART sono generatore CLK, registri a scorrimento I/O, buffer di trasmissione o ricezione, buffer del bus dati di sistema, logica di controllo di lettura o scrittura, ecc. |

Analizzatore di protocollo JTAG

L'analizzatore di protocollo JTAG come PGY-JTAG-EX-PD è un tipo di analizzatore di protocollo che include alcune funzionalità per acquisire ed eseguire il debug della comunicazione tra host e progettazione in fase di test. Questo tipo di analizzatore è lo strumento principale che consente agli ingegneri di test e progettazione di testare i particolari progetti di JTAG per le sue specifiche predisponendo il PGY-JTAG-EX-PD come Master o Slave per generare traffico JTAG e decodificare i pacchetti di decodifica del Protocollo del Joint Test Action Group.

Caratteristiche

Le caratteristiche dell'analizzatore di protocollo JTAG includono quanto segue.

- Supporta fino a 25 MH di frequenze JTAG.

- Genera contemporaneamente traffico JTAG e decodifica del protocollo per il bus.

- Ha capacità master JTAG.

- Velocità dati JTAG variabili e Duty cycle.

- Ritardi TDI e TCK definiti dall'utente.

- Interfaccia USB 2.0 o 3.0 del computer host.

- Analisi degli errori all'interno della decodifica del protocollo

- Diagramma di temporizzazione del bus decodificato dal protocollo.

- Streaming continuo dei dati del protocollo al computer host per fornire un buffer di grandi dimensioni.

- Elenco delle attività del protocollo.

- A varie velocità, è possibile scrivere uno script di esercizio per combinare la generazione di più frame di dati.

Diagramma temporale

Il diagramma temporale del JTAG il protocollo è mostrato di seguito. Nel diagramma seguente, il pin TDO rimane nella condizione di alta impedenza tranne che durante uno stato del controller shift-IR/shift-DR.

Nelle condizioni del controller shift-IR e Shift-DR, il pin TDO viene aggiornato sul fronte decrescente di TCK tramite Target e campionato sul fronte crescente di TCK tramite Host.

Entrambi i pin TDI e TMS vengono semplicemente campionati sul bordo crescente di TCK attraverso Target. Aggiornato sul bordo decrescente altrimenti TCK tramite Host.

Applicazioni

Il Applicazioni JTAG include il seguente.

- Il Joint Test Action Group viene spesso utilizzato nei processori per fornire il diritto di accesso alle loro funzioni di emulazione o debug.

- Tutti i CPLD e gli FPGA lo utilizzano come interfaccia per dare accesso alle loro funzioni di programmazione.

- Viene utilizzato per il test dei PCB senza accesso fisico

- Viene utilizzato per i test di produzione a livello di scheda.

Quindi, questo è tutto una panoramica di JTAG – configurazione pin, lavorare con le applicazioni. Lo standard industriale JTAG viene utilizzato per la verifica del progetto e per i test PCB dopo la produzione. Ecco una domanda per te, JTAG sta per?