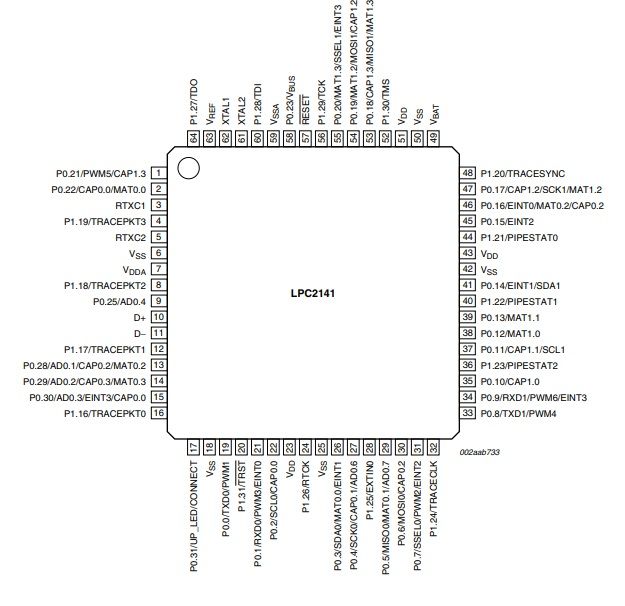

L'ARM (Advanced RISC Machine) ha lanciato diversi processori che hanno caratteristiche diverse così come i diversi core per un'ampia varietà di applicazioni. Il primo progetto di architettura ARM ha processori a 26 bit, ma ora ha raggiunto processori a 64 bit. L'espansione generale dei prodotti ARM non può essere classificata in alcune informazioni particolari. Ma i prodotti ARM possono essere compresi in base alla loro architettura. I processori della serie ARM standard disponibili sul mercato iniziano da ARM7 a ARM11. Questi processori hanno diverse caratteristiche come cache, memoria Data Tightly Coupled, MPU, MMU, ecc. Alcune delle serie di processori ARM ampiamente conosciute sono ARM926EJ-S, ARM7TDMI e ARM11 MPCore. Questo articolo è destinato in particolare alla panoramica dell'architettura del microcontrollore LPC2148 basato su ARM7, che fornirà brevi informazioni su il microcontrollore architettura.

Architettura del microcontrollore LPC2148 basata su ARM7

L'ARM7 è un generico a 32 bit microprocessore e offre alcune delle funzionalità come un ridotto consumo energetico e prestazioni elevate. L'architettura di un ARM dipende da principi di RISC . Il meccanismo di decodifica associato, così come il set di istruzioni RISC, sono molto facili se confrontati con CISC microprogrammato - Computer con set di istruzioni complessi.

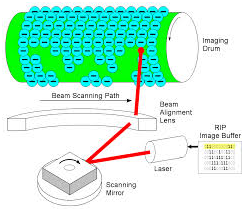

Il metodo Pipeline viene utilizzato per elaborare tutti i blocchi in architettura. In generale, viene eseguito un singolo set di istruzioni, quindi viene tradotto il suo discendente e un 3rd-l'istruzione viene ottenuta dalla memoria.

Un'esclusiva progetto architettonico di ARM7 si chiama Thumb, ed è perfettamente adatto per applicazioni ad alto volume dove la compattezza del codice è una questione. L'ARM7 utilizza anche un'architettura esclusiva chiamata Thumb. Lo rende perfettamente adatto a diverse applicazioni per limitazioni di memoria in cui la densità del codice è una questione.

Architettura del microcontrollore basato su ARM7 (LPC2148)

Fonti di interrupt

Ogni dispositivo periferico è costituito da una singola linea di interrupt alleata al VIC (controller di interrupt vettoriale), sebbene al suo interno possa avere diversi flag di interrupt. I flag di interrupt individuali possono anche indicare una o più risorse di interrupt.

Memoria di programma flash su chip

Il microcontrollore LPC2141 / 42/44/46/48 include una memoria flash come rispettivamente 32 kilobyte, kilobyte, 128 kilobyte e 256 kilobyte. Questa memoria flash può essere utilizzata sia per l'archiviazione dei dati che per il codice. La programmazione della memoria flash può essere effettuata nel sistema tramite la porta seriale.

L'applicazione del programma può anche essere cancellata mentre l'applicazione del programma è in esecuzione, consentendo flessibilità di miglioramenti del firmware sul campo di archiviazione dei dati, ecc. A causa della selezione di una soluzione architettonica per un bootloader su chip, la memoria disponibile per i microcontrollori LPC2141 / 42 / 44/46/48 è 32 kilobyte, kilobyte, 128 kilobyte, 256 kilobyte e 500 kilobyte. La memoria flash di questi microcontrollori offre 1, 00.000 cancellazioni per ciclo e la conservazione dei dati per molti anni.

Pin Connect Block

Questo blocco consente ai pin scelti del microcontrollore LPC2148 basato su ARM7 di avere diverse funzioni. I multiplexer può essere controllato dai registri di configurazione per consentire il collegamento tra il pin e le periferiche su chip.

Le periferiche devono essere accoppiate con i pin appropriati prima di essere attivate e prima che siano consentiti gli interrupt collegati. La funzionalità del microcontrollore può essere definita dal modulo di controllo dei pin mediante la selezione dei pin dei registri in un determinato ambiente hardware.

Dopo aver riorganizzato tutti i pin delle porte (porta 0 e porta 1) vengono disposti come i / p in base alle eccezioni fornite. Se il debug è consentito

Se il debug è consentito, i pin del JTAG indovineranno la funzionalità di JTAG. Se una traccia è consentita, i perni Trace indovineranno la funzionalità della traccia. I pin collegati ai pin I2C0 e I2C1 sono a drain aperto.

GPIO - Ingresso / uscita parallela per uso generico

I registri GPIO controllano i pin del dispositivo che non sono collegati a una particolare funzione periferica. I pin del dispositivo possono essere disposti come i / p [so o / ps. I singoli registri consentono di cancellare un numero qualsiasi di o / p contemporaneamente. Il valore del registro di uscita può essere riletto e le condizioni attuali dei pin della porta. Questi microcontrollori iniziano una funzione accelerata sui dispositivi LPC200.

I registri di input / output per scopi generici vengono spostati sul bus del processore utilizzato per il miglior tempo probabile di I / O.

- Questi registri sono byte indirizzabili.

- Il valore totale di una porta può essere

- Il valore completo della porta può essere scritto nell'unica istruzione

ADC a 10 bit (convertitore da analogico a digitale)

I microcontrollori come LPC2141 o 42 ne includono due Convertitori ADC , e questi sono solo a 10 bit ne hanno uno e l'LPC2144 / 46/48 ha due ADC, e questi sono solo ADC ad approssimazione lineare a 10 bit. Sebbene ADC0 includa 6 canali e ADC1 abbia 8 canali. Pertanto, il numero di i / ps ADC accessibili per LPC2141 o 42 è 6 e 14 per LPC2141 o 42.

DAC a 10 bit (convertitore da digitale ad analogico)

Il DAC consente a questi microcontrollori di produrre un o / p analogico modificabile e VRIFè il massimo output di a digitale in analogico voltaggio.

Controller dispositivo-USB 2.0

Il bus seriale universale è costituito da 4 fili e fornisce il supporto per la comunicazione tra un numero di periferiche e host. Questo controller consente la larghezza di banda dell'USB per il collegamento di dispositivi utilizzando un protocollo basato sul token.

Il bus supporta lo scollegamento dell'hot plug e la raccolta dinamica dei dispositivi. Ogni comunicazione viene avviata tramite il controller host. Questi microcontrollori sono progettati con un controller dell'apparato bus seriale universale che consente la sostituzione di dati a 12 Mbit / sec con un controller host USB.

UART

Questi microcontrollori includono due UART per la trasmissione e l'acquisizione di linee dati standard. Contrariamente ai microcontrollori precedenti (LPC2000), gli UART nei microcontrollori LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 avviano un generatore di baud rate parziale utilizzato per entrambi gli UART, consentendo a questi tipi di microcontrollori di raggiungere velocità di trasmissione tipiche come 115200 per ogni frequenza di cristallo su 2 MHz . Inoltre, le funzioni di controllo come CTS / RTS sono completamente eseguite nell'hardware.

Controller I / O seriale del bus I2C

Ogni microcontrollore da LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 include due I2C controller bus, e questo è bidirezionale. Il controllo inter-IC può essere eseguito con l'ausilio di due fili, ovvero SCL e SDA. Qui SDA e SCL sono la linea di clock seriale e la linea di dati seriale

Ogni apparecchio è identificato da un indirizzo individuale. Qui, trasmettitori e ricevitori possono funzionare in due modalità come modalità master / modalità slave. Si tratta di un bus multi-master, e può essere gestito da uno o più bus master ad esso collegati. Questi microcontrollori supportano velocità di trasmissione fino a 400 kbit / s.

Controller di ingresso / uscita seriale SPI

Questi microcontrollori includono un singolo controller SPI e sono destinati a gestire numerosi master e slave associati a un bus specificato.

Semplicemente un master e uno slave possono conversare sull'interfaccia durante la trasmissione dati specificata. Durante questo, il master trasmette costantemente un byte di dati verso lo slave, così come lo slave trasmette costantemente i dati verso il master.

Controller di ingresso / uscita seriale SSP

Questi microcontrollori contengono un singolo SSP e questo controller è in grado di elaborare un SPI, un bus Microwire o un SSI a 4 fili. Può comunicare con il bus di diversi master oltre che con gli slave

Ma semplicemente un particolare master, così come uno slave, può conversare sul bus durante una trasmissione dati specificata. Questo microcontrollore supporta trasferimenti full-duplex, da frame di dati a 4-16 bit utilizzati per il flusso di dati dal master-lo slave e dallo slave-il master.

Timer / contatori

Timer e contatori sono progettati per contare i cicli PCLK (orologio periferico) e opzionalmente producono interrupt basati su registri a 4 corrispondenze.

E comprende quattro i / ps di acquisizione per catturare il valore di un timer quando un segnale i / p cambia. È possibile scegliere diversi pin per eseguire una particolare acquisizione. Questi microcontrollori possono calcolare eventi esterni sugli ingressi di cattura se il minimo impulso esterno è equivalente. In questa disposizione, le linee di cattura inattive possono essere scelte come al solito i / ps di cattura con timer.

Watchdog Timer

Il timer watchdog viene utilizzato per ripristinare il microcontrollore in una ragionevole somma di tempo. Quando è consentito, il timer produrrà un ripristino di un sistema se il programma utente non riesce a ricaricare il timer in una somma di tempo fissa.

Orologio RTC in tempo reale

L'RTC ha lo scopo di fornire contatori per calcolare il tempo quando viene scelto il metodo di funzionamento inattivo o normale. L'RTC utilizza una piccola quantità di energia ed è progettato per opportuni accorgimenti alimentati a batteria in cui l'unità di elaborazione centrale non funziona costantemente

Controllo di potenza

Questi microcontrollori supportano due modalità di alimentazione condensata come la modalità di spegnimento e la modalità di inattività. In modalità Idle, l'esecuzione delle istruzioni è bilanciata fino a quando non si verifica un interrupt o un RST. Le funzioni della periferica mantengono il funzionamento durante la modalità inattiva e possono produrre interruzioni per far ripartire la CPU. La modalità inattiva rimuove l'energia utilizzata da CPU, controller, sistemi di memoria e bus interni.

In modalità di spegnimento, l'oscillatore è disattivato e l'IC non riceve orologi interni. I registri periferici, le condizioni del processore con i registri, i valori SRAM interni vengono conservati durante la modalità di spegnimento ei pin di uscita dei livelli logici del chip rimangono fissi.

Questa modalità può essere terminata e il processo comune può essere riavviato da interrupt specifici in grado di funzionare senza orologi. Poiché il funzionamento del chip è bilanciato, la modalità Power-down riduce l'utilizzo energetico del chip quasi a zero.

PWM -Pulse Width Modulator

I PWM si basano sul normale blocco del timer e rientrano in tutte le funzionalità, anche se semplicemente la funzione del modulatore di larghezza di impulso è fissata sui microcontrollori come LPC2141 / 42/44/46/48.

Il timer ha lo scopo di calcolare i cicli PCLK (orologio periferico) e opzionalmente produrre interrupt quando si verificano particolari valori del timer in base a registri di 7 corrispondenze e la funzione PWM dipende anche dagli eventi del registro di corrispondenza.

La capacità di controllare individualmente l'aumento e la diminuzione delle posizioni dei limiti consente di utilizzare la modulazione della larghezza dell'impulso per diverse applicazioni. Ad esempio, il tipico controllo del motore con multifase utilizza 3 uscite non sovrapposte di PWM mediante un controllo separato di ogni larghezza di impulso e posizioni.

Bus VPB

Il divisore VPB risolve l'associazione tra CCLK (clock del processore) e PCLK (clock utilizzato dai dispositivi periferici). Questo divisore viene utilizzato per due scopi. Il primo utilizzo è fornire le periferiche dal PCLK preferito utilizzando il bus VPB in modo che possano funzionare alla velocità selezionata del processore ARM. Per fare ciò, questa velocità del bus può essere ridotta la frequenza di clock del processore da 1⁄ 2 -1⁄ 4.

Perché questo bus deve funzionare accuratamente all'accensione e lo stato predefinito a RST (reset) è che il bus funzioni a 1⁄4 della frequenza di clock del processore. Il secondo utilizzo è quello di consentire il risparmio energetico ogni volta che un'applicazione non necessita di alcuna periferica per funzionare alla velocità del processore completa. Poiché il divisore VPB è associato all'uscita di PLL, questo rimane attivo per tutta la modalità inattiva.

Emulazione e debug

Il microcontrollore (LPC2141 / 42/44/46/48) mantiene l'emulazione e il debug tramite porta seriale-JTAG. Una porta di traccia consente di tracciare l'esecuzione del programma. Le funzioni di traccia e i concetti di debug sono multiplexati con port1 e GPIO.

Codice di sicurezza

La funzione di sicurezza del codice di questi microcontrollori LPC2141 / 42/44/46/48 consente a una funzione di controllare se può essere protetto o sottoposto a debug dall'ispezione.

Quindi, questo è tutto sull'architettura del microcontrollore LPC2148 basata su ARM7. Dall'articolo sopra, infine, possiamo concludere che ARM è un'architettura utilizzata in numerosi processori e microcontrollori. Ecco una domanda per te, qual è l'architettura di un processore ARM?