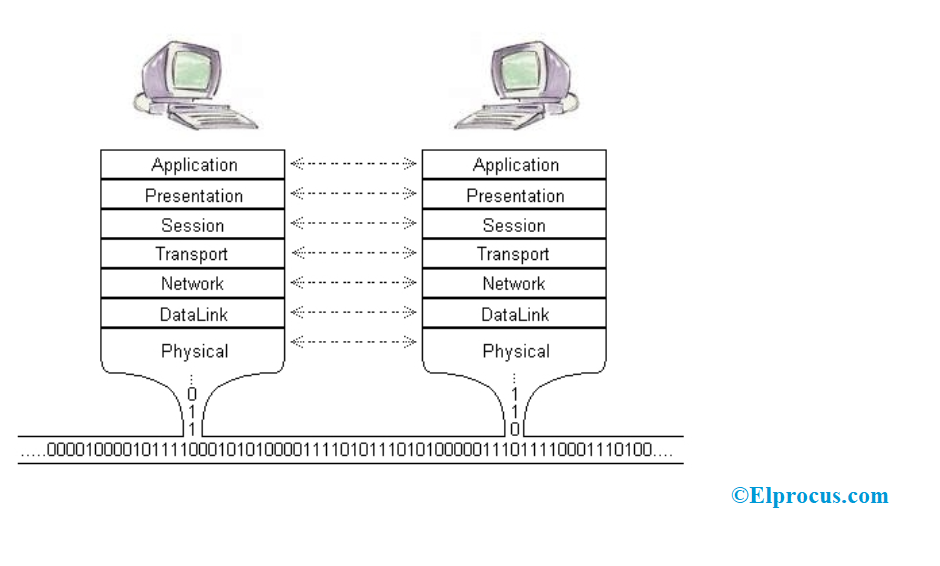

Le funzionalità più potenti e importanti sono le interruzioni in Microcontrollore 8051 . Nella maggior parte dei processi in tempo reale, per gestire correttamente determinate condizioni, l'attività effettiva deve essere interrotta per un po 'di tempo - richiede l'azione richiesta - e quindi deve tornare all'attività principale. Per eseguire questo tipo di programmi, sono necessari degli interrupt. È completamente diverso dal metodo di polling in cui il processore deve controllare in sequenza ogni dispositivo e chiedere se il servizio è richiesto o meno mentre consuma più tempo del processore.

Si interrompe nel microcontrollore 8051

Gli interrupt nel microcontrollore 8051 sono più desiderabili per ridurre il controllo regolare dello stato dei dispositivi interfacciati o dei dispositivi integrati. L'interrupt è un evento che sospende temporaneamente il programma principale, passa il controllo a una sezione di codice speciale, esegue la funzione correlata all'evento e riprende il flusso del programma principale dal punto in cui era stato interrotto.

Gli interrupt sono di diversi tipi come software e hardware, mascherabili e non mascherabili, interrupt fissi e vettoriali e così via. Interrupt Service Routine (ISR) entra in scena quando si verifica l'interruzione, quindi dice al processore di intraprendere l'azione appropriata per l'interruzione e, dopo l'esecuzione dell'ISR, il controller passa al programma principale.

Tipi di interrupt nel microcontrollore 8051

Il microcontrollore 8051 può riconoscere cinque diversi eventi che provocano l'interruzione del programma principale dalla normale esecuzione. Queste cinque fonti di interruzioni nell'8051 sono:

- Timer 0 overflow interrupt - TF0

- Interrupt di overflow del timer 1 - TF1

- Interrupt di processo esterno - INT0

- Interrupt di processo esterno - INT1

- Interruzione della comunicazione seriale - RI / TI

Gli interrupt Timer e Serial sono generati internamente dal microcontrollore, mentre gli interrupt esterni sono generati da ulteriori dispositivi di interfacciamento o interruttori che sono collegati esternamente al microcontrollore. Questi interrupt esterni possono essere attivati dal fronte o dal livello. Quando si verifica un interrupt, il microcontrollore esegue la routine del servizio di interrupt in modo che la posizione di memoria corrisponda all'interrupt che lo abilita. L'interrupt corrispondente alla posizione di memoria è indicato nella tabella del vettore di interrupt di seguito.

Tabella dei vettori di interruzione

Struttura degli interrupt del microcontrollore 8051

Al momento del 'RESET' tutti gli interrupt vengono disabilitati e quindi tutti questi interrupt devono essere abilitati da un software. In tutti questi cinque interrupt, se uno o tutti sono attivati, questo imposta i flag di interrupt corrispondenti come mostrato in figura. Tutti questi interrupt possono essere impostati o cancellati per bit in qualche registro di funzione speciale che è Interrupt Enabled (IE), e questo a sua volta dipende dalla priorità, che viene eseguita dal registro di priorità degli interrupt IP.

Struttura di interrupt del microcontrollore 8051

Registro di abilitazione interrupt (IE): Questo registro è responsabile dell'abilitazione e della disabilitazione dell'interrupt. È un registro indirizzabile a bit in cui EA deve essere impostato su uno per abilitare gli interrupt. Il bit corrispondente in questo registro abilita particolari interrupt come timer, ingressi esterni e seriali. Nel registro IE sottostante, il bit corrispondente a 1 attiva l'interrupt e 0 disabilita l'interrupt.

Registro di abilitazione interrupt (IE)

Registro priorità interrupt (IP): È anche possibile modificare i livelli di priorità degli interrupt impostando o cancellando il bit corrispondente nel registro di priorità degli interrupt (IP) come mostrato in figura. Ciò consente all'interruzione a bassa priorità di interrompere l'interruzione ad alta priorità, ma impedisce l'interruzione da parte di un altro interruzione a bassa priorità. Allo stesso modo, l'interrupt ad alta priorità non può essere interrotto. Se queste priorità di interrupt non sono programmate, il microcontrollore viene eseguito in modo predefinito e il suo ordine è INT0, TF0, INT1, TF1 e SI.

Registro IP

Registro TCON: Oltre ai due registri precedenti, il registro TCON specifica il tipo di interrupt esterno al microcontrollore 8051, come mostrato in figura. I due interrupt esterni, attivati dal fronte o dal livello, specificati da questo registro da un insieme o cancellati da bit appropriati in esso. Ed è anche un registro bit indirizzabile.

Registro TCON

Interruzione della programmazione in 8051

1. Programmazione dell'interruzione del timer

Gli interrupt del timer 0 e del timer 1 sono generati dai bit di registro del timer TF0 e TF1. Queste interruzioni programmazione tramite codice C. coinvolge:

- Selezione del timer configurando il registro TMOD e la sua modalità di funzionamento.

- Scegliere e caricare i valori iniziali di TLx e THx per le modalità appropriate.

- Abilitazione dei registri IE e del bit del timer corrispondente in esso.

- Impostazione del bit di esecuzione del timer per avviare il timer.

- Scrittura della subroutine per il timer per il tempo richiesto e cancellazione del valore del timer TRx alla fine della subroutine.

Programmazione interruzione timer

2. Programmazione di interrupt hardware esterno

I microcontrollori 8051 sono costituiti da due interrupt hardware esterni: INT0 e INT1 come discusso in precedenza. Questi sono abilitati al pin 3.2 e al pin 3.3. Questi possono essere attivati dal fronte o attivati dal livello. Nel trigger di livello, il basso sul pin 3.2 abilita l'interrupt, mentre sul pin 3.2 - la transizione da alto a basso abilita l'interrupt attivato dal fronte. Questo trigger sul fronte o trigger sul livello viene deciso dal registro TCON che è stato discusso sopra. Il procedura di programmazione in 8051 è come segue:

- Abilita il bit corrispondente di interrupt esterno nel registro IE.

- Se si tratta di trigger di livello, è sufficiente scrivere la subroutine appropriata per questo interrupt, oppure abilitare il bit di registro TCON corrispondente all'interrupt attivato dal fronte, sia esso INT0 o INT1.

Programmazione interrupt hardware esterno

3. Programmazione dell'interruzione della comunicazione seriale

Quando è necessario inviare o ricevere dati, si verificano interruzioni della comunicazione seriale. Poiché un bit di interrupt è impostato per entrambi i flag TI (Transfer Interrupt) e RI (Receiver Interrupt), la routine del servizio di interrupt deve esaminare questi flag per conoscere l'interrupt effettivo.

L'operazione logica OR di questi due flag (RI e TI) causa questo interrupt e viene cancellato solo dal software. Qui, uno speciale registro SCON viene utilizzato per il controllo comunicazione funzionamento abilitando i bit corrispondenti in esso.

- Configurare il registro IE per abilitare l'interrupt seriale

- Configurare il registro SCON per la ricezione o il trasferimento dell'operazione

- Scrivere la subroutine per questo interrupt con la funzione appropriata e cancellare i flag TI o RI con in questa routine.

Programmazione di interrupt seriale

Si tratta di interrupt nel microcontrollore 8051, tipi, loro struttura e programmazione. Spero che tu possa aver ricevuto buone informazioni da questo articolo. Inoltre, puoi scriverci nella sezione commenti sottostante per l'implementazione in tempo reale di progetti di microcontrollore in modo da poterti assistere per una migliore esperienza pratica.

Crediti fotografici

- Si interrompe nel microcontrollore 8051 di engineergarage

- Interrompi tabella vettoriale di 8051projects

- Interrompi la struttura del microcontrollore 8051 di spazzola

- Abilita interrupt (IE) Registrati per elettroni

- Registro IP di circuiti oggi

- TCON Registrati da circuiti oggi