Questo articolo spiega il generazione della modulazione della larghezza di impulso segnali con duty cycle variabile su FPGA utilizzando VHDL. PWM ha una frequenza fissa e una tensione variabile. Questo articolo illustra anche il Digital Clock Manager per diminuire la frequenza di clock diminuendo l'inclinazione del segnale di clock. Una frequenza fissa viene utilizzata per produrre i dati di ingresso che producono i segnali PWM utilizzando un comparatore. Le aziende elettroniche progettano l'hardware dedicato ai loro prodotti con i loro standard e protocolli, il che rende difficile per gli utenti finali riconfigurare l'hardware secondo le loro esigenze. Questo requisito per l'hardware ha portato alla crescita di un nuovo segmento configurabile dal cliente circuiti integrati programmabili sul campo chiamati FPGA .

Modulazione di larghezza di impulso (PWM)

La modulazione di larghezza di impulso è ampiamente utilizzata nelle applicazioni di comunicazione e sistemi di controllo . La modulazione della larghezza di impulso può essere generata utilizzando diversi approcci nei sistemi di controllo. Qui, in questo articolo, PWM viene generato utilizzando VHDL (Hardware Description Language) e implementato su FPGA. L'implementazione del PWM su FPGA può elaborare i dati più velocemente e l'architettura del controller può essere ottimizzata per lo spazio o la velocità.

PWM è una tecnica per fornire '0' logico e '1' logico per un periodo di tempo controllato. È una sorgente di segnale che prevede la modulazione del suo ciclo di lavoro per controllare la quantità di potenza inviata al carico. In PWM, il periodo di tempo dell'onda quadra viene mantenuto costante e il tempo per il quale il segnale rimane ALTO viene variato.

Il PWM genera gli impulsi sulla sua uscita in modo tale che il valore medio di HIGH e LOW sia proporzionale all'ingresso PWM. Il ciclo di lavoro del segnale può essere variato. Un segnale PWM è un'onda quadra a periodo costante con ciclo di lavoro variabile. Cioè, la frequenza del segnale PWM è costante, ma il periodo di tempo del segnale rimane alto e varia come mostrato.

Segnale PWM

VHDL

VHDL è un linguaggio, utilizzato per descrivere il comportamento di progetti di circuiti digitali . VHDL è utilizzato da industrie e accademici ai fini della simulazione di circuiti digitali. Il suo design può essere simulato e tradotto nella forma adatta per l'implementazione nell'hardware.

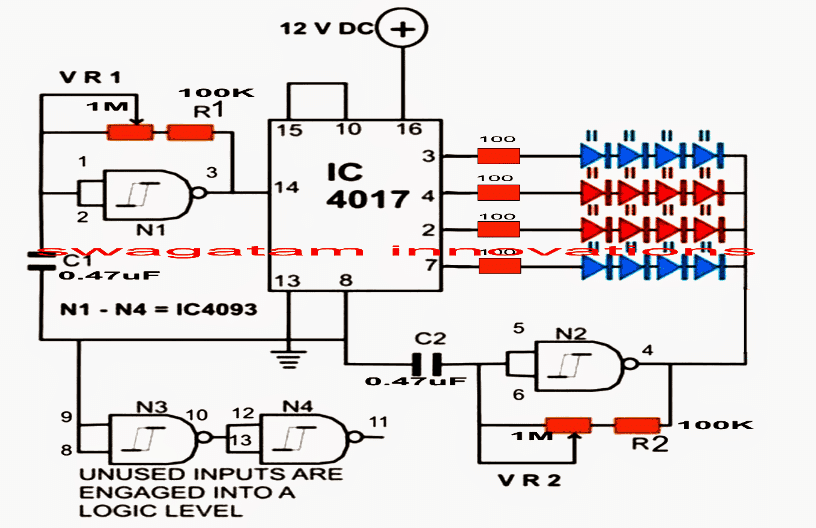

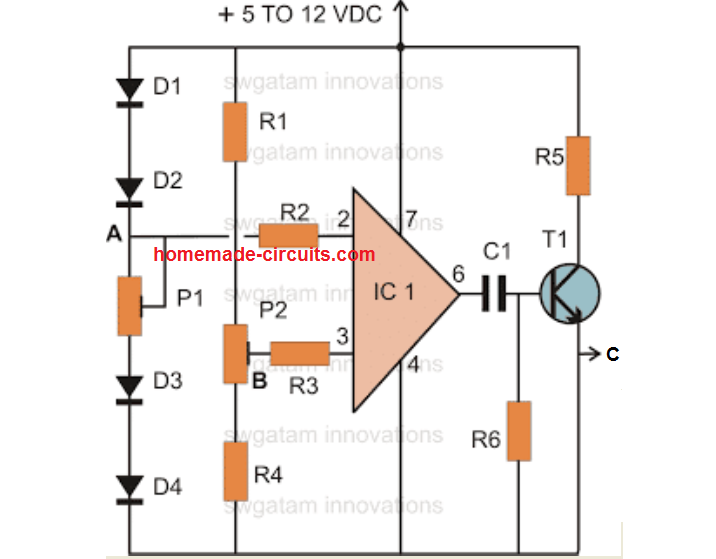

Architettura PWM

Per produrre i dati di ingresso per generare il PWM utilizzando un contatore a corsa libera a N bit ad alta velocità, la cui uscita viene confrontata con l'uscita del registro e memorizza il ciclo di lavoro di ingresso desiderato con l'aiuto del comparatore. Il comparatore l'uscita è impostata a 1 quando entrambi questi valori sono uguali. Questa uscita del comparatore viene utilizzata per impostare il latch RS. Il segnale di overflow dal contatore viene utilizzato per ripristinare il latch RS. Il uscita del latch RS fornisce l'uscita PWM desiderata. Questo segnale di overflow viene utilizzato anche per caricare il nuovo duty cycle a N bit nel registro. PWM ha una frequenza fissa e una tensione variabile. Questo valore di tensione cambia da 0 V a 5 V.

Segnale PWM con duty cycle variabile

Il PWM di base genera i segnali, che fornisce l'uscita del PWM, richiede un comparatore che confronta due valori. Il primo valore rappresenta il segnale quadrato generato dal contatore N bit e il secondo valore rappresenta il segnale quadrato che contiene le informazioni sul ciclo di lavoro. Il contatore genera il segnale di carico ogni volta che si verifica un overflow. Quando il segnale di carico diventa attivo, il registro carica il nuovo valore del duty cycle. Il segnale di carico viene utilizzato anche per ripristinare il latch. L'uscita latch è un segnale PWM. Questo varia con la variazione del valore del ciclo di lavoro.

Cos'è FPGA?

L'FPGA è un array di porte programmabili sul campo. È un tipo di dispositivo ampiamente utilizzato nei circuiti elettronici. Gli FPGA lo sono dispositivi semiconduttori che contengono blocchi logici programmabili e circuiti di interconnessione. Può essere programmato o riprogrammato per la funzionalità richiesta dopo la produzione.

FPGA

Nozioni di base su FPGA

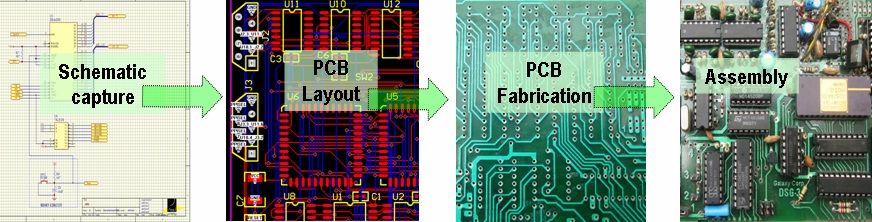

Quando viene prodotto un circuito stampato e se contiene un FPGA come parte di esso. Questo viene programmato durante il processo di produzione e può essere riprogrammato in seguito per creare un aggiornamento o apportare le modifiche necessarie. Questa caratteristica di FPGA lo rende unico da ASIC. I circuiti integrati per applicazioni specifiche (ASIC) sono realizzati su misura per attività di progettazione specifiche. In passato gli FPGA venivano utilizzati per sviluppare design a bassa velocità, complessità e volume, ma oggi FPGA spingerà facilmente la barriera delle prestazioni fino a 500 MHz.

Nei microcontrollori, il chip è progettato per un cliente e deve scrivere il software e compilarlo in un file esadecimale da caricare sul microcontrollore. Questo software può essere facilmente sostituito poiché è memorizzato nella memoria flash. Negli FPGA, non esiste un processore per eseguire il software e siamo noi a progettare il circuito. Possiamo configurare un FPGA semplice come un gate AND o un complesso come un processore multi-core. Per creare un design scriviamo Hardware Description Language (HDL), che è di due tipi: Verilog e VHDL. Quindi l'HDL viene sintetizzato in un file bit utilizzando un BITGEN per configurare l'FPGA. L'FPGA memorizza la configurazione nella RAM, ovvero la configurazione viene persa quando non c'è connettività di alimentazione. Pertanto, devono essere configurati ogni volta che viene fornita l'alimentazione.

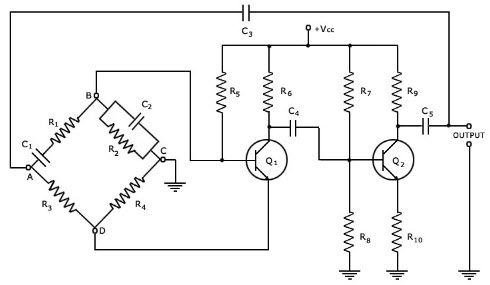

Architettura di FPGA

Gli FPGA sono chip di silicio prefabbricati che possono essere programmati elettricamente per implementare progetti digitali. Il primo FPGA basato su memoria statica chiamato SRAM viene utilizzato per configurare sia la logica che l'interconnessione utilizzando un flusso di bit di configurazione. Il moderno EPGA di oggi contiene circa 3,30.000 blocchi logici e circa 1.100 ingressi e uscite.

Architettura FPGA

L'architettura di FPGA è costituita da tre componenti principali

- Blocchi logici programmabili, che implementano funzioni logiche

- Routing programmabile (interconnessioni), che implementa le funzioni

- Blocchi I / O, utilizzati per effettuare connessioni off-chip

Applicazioni dei segnali PWM

I segnali PWM sono ampiamente utilizzati per le applicazioni di controllo. Come il controllo di motori DC, valvole di controllo, pompe, idraulica, ecc. Ecco le poche applicazioni dei segnali PWM.

- Impianti di riscaldamento con tempi lenti da 10 a 100Hz o superiori.

- Motori elettrici CC da 5 a 10 KHz

- Alimentatori o amplificatori audio da 20 a 200 KHz.

Questo articolo riguarda interamente il generazione di segnali PWM con duty cycle variabile utilizzando FPGA. Inoltre, per qualsiasi aiuto su progetti elettronici o dubbi su questo articolo, puoi contattarci commentando la sezione commenti riportata di seguito.