Il transistor ad effetto di campo (FET) è un dispositivo elettronico in cui un file campo elettrico viene utilizzato per regolare il flusso di corrente. Per implementare ciò, viene applicata una differenza di potenziale tra i terminali di gate e source del dispositivo, che altera la conduttività tra i terminali di drain e source provocando il flusso di una corrente controllata attraverso questi terminali.

Si chiamano FET transistor unipolari perché sono progettati per funzionare come dispositivi a portante singolo. Sono disponibili diversi tipi di transistor ad effetto di campo.

Simbolo

I simboli grafici per i JFET a canale n e canale P possono essere visualizzati nelle figure seguenti.

È possibile notare chiaramente che i segni di freccia che puntano verso l'interno per il dispositivo a canale n indicano la direzione in cui IG(corrente di gate) dovrebbe fluire quando la giunzione p-n era polarizzata in avanti.

Nel caso di un dispositivo a canale p le condizioni sono identiche tranne la differenza nella direzione del simbolo della freccia.

Differenza tra FET e BJT

Il transistor ad effetto di campo (FET) è un dispositivo a tre terminali progettato per una vasta gamma di applicazioni circuitali che completano, ad un ottimo livello, quelle del transistor BJT.

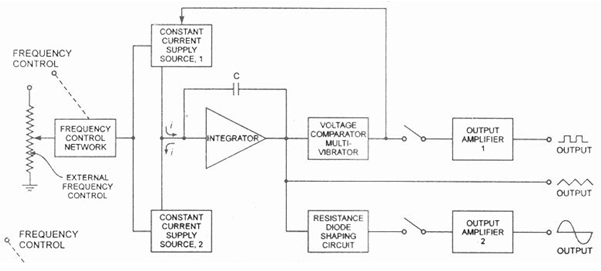

Mentre troverai differenze significative tra BJT e JFET, ci sono in realtà diverse caratteristiche di corrispondenza di cui parleremo nelle discussioni seguenti. La principale distinzione tra questi dispositivi è che BJT è un dispositivo controllato in corrente come rappresentato in Fig. 5.1a, mentre il transistor JFET è un dispositivo controllato in tensione come indicato in Fig. 5.1b.

In parole povere, l'attuale ICin Fig. 5.1a è una funzione immediata del livello di IB. Per il FET la corrente I è una funzione della tensione VGSdato al circuito di ingresso come mostrato in Fig. 5.1b.

In entrambi i casi la corrente del circuito di uscita sarà regolata da un parametro del circuito di ingresso. In una situazione un livello di corrente e nell'altra una tensione applicata.

Proprio come npn e pnp per i transistor bipolari, troverai transistor ad effetto di campo a canale n e p. Ma, dovresti ricordare che il transistor BJT è un dispositivo bipolare il prefisso bi- indica che il livello di conduzione è una funzione di due portatori di carica, elettroni e lacune.

Il FET d'altra parte è un file dispositivo unipolare ciò dipende esclusivamente dalla conduzione dell'elettrone (canale n) o del foro (canale p).

La frase 'effetto di campo' può essere spiegata in questo modo: tutti noi siamo consapevoli del potere di un magnete permanente di attirare la limatura di metallo verso il magnete senza alcun contatto fisico. In modo del tutto simile all'interno del FET un campo elettrico viene creato dalle cariche esistenti che influenzano il percorso di conduzione del circuito di uscita senza avere alcun contatto diretto tra le grandezze regolanti e controllate. Probabilmente una delle caratteristiche più cruciali del FET è la sua alta impedenza di ingresso.

Variando da una magnitudine da 1 a molte centinaia di megaohm, supera in modo significativo i normali intervalli di resistenza di ingresso delle configurazioni BJT, un attributo estremamente importante durante lo sviluppo di modelli di amplificatori CA lineari.

Tuttavia, il BJT ha una maggiore sensibilità alle variazioni del segnale di ingresso. Ciò significa che la variazione della corrente di uscita è comunemente significativamente maggiore per i BJT rispetto ai FET per la stessa quantità di variazione delle loro tensioni di ingresso.

Per questo motivo, i guadagni di tensione CA standard per gli amplificatori BJT possono essere molto più alti rispetto ai FET.

In generale, i FET sono notevolmente più resistenti dal punto di vista termico dei BJT e spesso hanno una struttura di dimensioni inferiori rispetto ai BJT, il che li rende specificamente adatti per l'incorporamento come circuito integrato (IC)patatine fritte.

Le caratteristiche strutturali di alcuni FET, d'altra parte, possono consentire loro di essere più sensibili ai contatti fisici rispetto ai BJT.

Più relazione BJT / JFET

- Per un BJT VESSERE= 0,7 V è il fattore importante per avviare un'analisi della sua configurazione.

- Allo stesso modo, il parametro IG= 0 A è comunemente la prima cosa considerata per l'analisi di un circuito JFET.

- Per la configurazione BJT, IBè spesso il primo fattore che diventa necessario determinare.

- Allo stesso modo, per il JFET, è tipicamente il VGS.

In questo articolo ci concentreremo sui JFET o transistor a effetto di campo a giunzione, nel prossimo articolo parleremo del transistor a effetto di campo o MOS-FET.

COSTRUZIONE E CARATTERISTICHE DEI JFET

Come abbiamo appreso all'inizio, un JFET ha 3 derivazioni. Uno di loro controlla il flusso di corrente tra gli altri due.

Proprio come i BJT, anche nei JFET il dispositivo a canale n è utilizzato in modo più prominente rispetto alle controparti a canale p, poiché i dispositivi n tendono a essere più efficienti e facili da usare rispetto al dispositivo p.

Nella figura seguente possiamo vedere la struttura di base o la costruzione di un JFET a canale n. Possiamo vedere che la composizione di tipo n forma il canale principale attraverso i livelli di tipo p.

La parte superiore del canale di tipo n è collegata tramite un contatto ohmico con un terminale denominato drain (D), mentre la sezione inferiore dello stesso canale è collegata anche tramite un contatto ohmico con un altro terminale denominato source (S).

La coppia di materiali di tipo p sono collegati tra loro con il terminale denominato gate (G). Essenzialmente troviamo che i terminali di drain e source sono uniti alle estremità del canale di tipo n. Il terminale di gate è unito a una coppia di materiale a canale P.

Quando non c'è tensione applicata su un jfet, le sue due giunzioni p-n sono prive di condizioni di polarizzazione. In questa situazione esiste una regione di esaurimento su ciascuna giunzione come indicato nella figura sopra, che assomiglia molto a una regione p-n del diodo senza polarizzazione.

Analogia dell'acqua

Le operazioni di funzionamento e controllo di un JFET possono essere comprese attraverso la seguente analogia con l'acqua.

Qui, la pressione dell'acqua può essere confrontata con l'ampiezza della tensione applicata dallo scarico alla sorgente.

Il flusso dell'acqua può essere paragonato al flusso degli elettroni. La bocca del rubinetto imita il terminale di sorgente del JFET, mentre la porzione superiore del rubinetto in cui l'acqua è forzata raffigura lo scarico del JFET.

La manopola tap si comporta come il Gate del JFET. Con l'aiuto di un potenziale di ingresso controlla il flusso di elettroni (carica) dallo scarico alla sorgente, proprio come la manopola del rubinetto controlla il flusso dell'acqua sull'apertura della bocca.

Dalla struttura JFET possiamo vedere che i terminali di drain e source sono alle estremità opposte del canale n, e poiché il termine è basato sul flusso di elettroni possiamo scrivere:

VGS= 0 V, VDSQualche valore positivo

Nella Fig 5.4 possiamo vedere una tensione positiva VDSapplicato attraverso il canale n. Il terminale di gate è direttamente unito alla sorgente per creare una condizione VGS= 0V. Ciò consente ai terminali di gate e di source di avere un potenziale identico e si traduce in una regione di esaurimento dell'estremità inferiore di ciascun materiale p, esattamente come si vede nel primo diagramma sopra con una condizione di non polarizzazione.

Non appena una tensione VDD(= VDS), gli elettroni vengono trascinati verso il terminale di drain, generando il flusso convenzionale di corrente ID, come indicato in Fig 5.4.

La direzione del flusso della carica rivela che la corrente di drain e source sono uguali in grandezza (I.D= IS). Secondo le condizioni rappresentate in Fig 5.4, il flusso della carica sembra abbastanza libero, e solo influenzato dalla resistenza del canale n tra drain e source.

Si può osservare che la regione di esaurimento è più grande intorno alla sezione superiore di entrambi i materiali di tipo p. Questa differenza di dimensione della regione è idealmente spiegata nella Fig. 5.5. Immaginiamo di avere una resistenza uniforme nel canale n, questa potrebbe essere suddivisa fino alle sezioni indicate in Fig. 5.5.

L'attuale IDpuò costruire gli intervalli di tensione attraverso il canale come indicato nella stessa figura. Di conseguenza, la regione superiore del materiale di tipo p sarà polarizzata inversamente di un livello di circa 1,5 V, con la regione inferiore semplicemente polarizzata inversamente di 0,5 V.

Il punto in cui la giunzione p-n è polarizzata inversamente lungo l'intero canale dà origine a una corrente di gate con zero ampere come mostrato nella stessa figura. Questa caratteristica che porta a I.G= 0 A è una caratteristica importante del JFET.

Come VDSil potenziale è aumentato da 0 a qualche volt, la corrente aumenta secondo la legge di Ohm e il grafico di I.Dlinea 5DSpuò apparire come mostrato in Fig. 5.6.

La rettilineità comparativa del tracciato mostra che per le regioni di valore basso di VDS, la resistenza è sostanzialmente uniforme. Come VDSsale e si avvicina a un livello noto come VP nella Fig. 5.6, le regioni di esaurimento si allargano come indicato nella Fig. 5.4.

Ciò si traduce in un apparente abbassamento della larghezza del canale. La diminuzione del percorso di conduzione porta all'aumento della resistenza dando origine alla curva di Fig. 5.6.

Più la curva diventa orizzontale, maggiore è la resistenza, indicando che la resistenza sta arrivando verso ohm 'infiniti' nella regione orizzontale. Quando VDSaumenta in una misura in cui sembrerebbe che le due regioni di esaurimento potrebbero 'entrare in contatto' come mostrato in Fig. 5.7, dà origine a una situazione nota come pinch-off.

L'importo di cui VDSsviluppa questa situazione si chiama pizzicare tensione ed è simboleggiato da VPcome presentato in Fig. 5.6. In generale, la parola pinch-off è fuorviante perché implica l'attuale IDviene 'pizzicato' e scende a 0 A. Come dimostrato nella Fig. 5.6, in questo caso non sembra evidente. ioDmantiene un livello di saturazione caratterizzato come I.DSSin Fig. 5.6.

La verità è che un canale molto piccolo continua ad esistere, con una corrente di concentrazione significativamente alta.

Il punto in cui l'ID non scende pizzicare e preserva il livello di saturazione come indicato in Fig. 5.6 viene confermato con la seguente dimostrazione:

Poiché non c'è corrente di drenaggio, si elimina la possibilità di diversi livelli di potenziale attraverso il materiale del canale n per determinare la quantità variabile di polarizzazione inversa lungo la giunzione p-n. Il risultato finale è la perdita della distribuzione della regione di esaurimento che si è innescata pizzicare iniziare con.

Man mano che aumentiamo VDSsopra VP, la regione di stretto contatto in cui le due regioni di esaurimento si incontreranno l'una con l'altra aumenta di lunghezza lungo il canale. Tuttavia, il livello ID continua ad essere sostanzialmente invariato.

Così il momento VDSè maggiore di Vp, il JFET acquisisce le caratteristiche di sorgente di corrente.

Come dimostrato in Fig 5.8, la corrente in un JFET è determinata a I.D= IDSS, ma la tensione VDSmaggiore di VP è stabilito dal carico collegato.

La selezione della notazione IDSS si basa sul fatto che è la corrente Drain to Source ad avere un collegamento in cortocircuito attraverso gate to source.

Ulteriori indagini ci danno la seguente valutazione:

ioDSSè la corrente di drain più alta per un JFET ed è stabilita dalle condizioni VGS= 0 V e VDS> | VP |.

Notare che in Fig. 5.6 VGSè 0V per l'intero tratto della curva. Nelle sezioni seguenti impareremo come gli attributi della Fig 5.6 vengono influenzati dal livello di VGSè vario.

VGS <0V

La volatage applicata attraverso il gate e la sorgente è indicata come VGS, che è responsabile del controllo delle operazioni JFET.

Se prendiamo l'esempio di un BJT, proprio come le curve di ICvs VQUESTOsono determinati per vari livelli di IB, allo stesso modo le curve di IDvs VDSper vari livelli di VGSpuò essere creato per una controparte JFET.

Per questo il terminale di gate è impostato su un potenziale inferiore continuo al di sotto del livello del potenziale di sorgente.

Facendo riferimento alla Fig. 5.9 sotto, viene applicato un -1V attraverso i terminali gate / source per una V ridottaDSlivello.

L'obiettivo del bias potenziale negativo VGSè quello di sviluppare regioni di esaurimento simili alla situazione di VGS= 0, ma a V notevolmente ridottaDS.

Ciò fa sì che il gate raggiunga un punto di saturazione con livelli inferiori di VDScome indicato in Fig. 5.10 (VGS= -1V).

Il livello di saturazione corrispondente per IDpuò essere ridotto e in realtà continua a diminuire come VGSè reso più negativo.

Puoi vedere chiaramente in Fig. 5.10 come la tensione di pinch-off continua a scendere con una forma parabolica come VGSdiventa sempre più negativo.

Infine, quando VGS= -Vp, diventa sufficientemente negativo per stabilire un livello di saturazione che alla fine è 0 mA. A questo livello, il JFET è completamente 'spento'.

Il livello di VGSche causa ioDper raggiungere 0 mA è caratterizzato da VGS= VP, in cui VPè una tensione negativa per i dispositivi a canale n e una tensione positiva per i JFET a canale p.

Comunemente, potresti trovare la maggior parte dei fogli dati JFET visualizzati pizzicare tensione specificata come VGS (spento)invece di VP.

L'area sul lato destro del luogo di pinch-off nella figura sopra è il luogo convenzionalmente utilizzato negli amplificatori lineari per ottenere un segnale privo di distorsioni. Questa regione è generalmente chiamata regione di corrente costante, saturazione o amplificazione lineare.

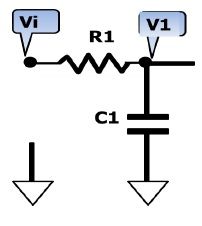

Resistore controllato in tensione

L'area che si trova sul lato sinistro del luogo di pinch-off nella stessa figura, è chiamata regione ohmica o regione di resistenza controllata dalla tensione.

In questa regione il dispositivo può infatti funzionare come un resistore variabile (ad esempio in un'applicazione di controllo automatico del guadagno), con la sua resistenza controllata attraverso il potenziale gate / source applicato.

Puoi vedere che la pendenza di ciascuna delle curve che indica anche la resistenza di drain / source del JFET per VDS

Man mano che aumentiamo il VGS con potenziale negativo, la pendenza di ciascuna curva diventa sempre più orizzontale, mostrando livelli di resistenza proporzionalmente crescenti.

Siamo in grado di ottenere una buona approssimazione iniziale del livello della resistenza rispetto alla tensione VGS, tramite la seguente equazione.

P-Channel JFET funzionante

Il layout interno e la costruzione di un JFET a canale p sono esattamente identici alla controparte a canale n, tranne per il fatto che le regioni dei materiali di tipo pe n sono invertite, come mostrato di seguito:

Le direzioni del flusso di corrente possono anche essere viste come invertite, insieme alle polarità effettive della tensione VGS e VDS. In caso di un JFET a canale p, il canale verrà limitato in risposta all'aumento del potenziale positivo attraverso il gate / source.

La notazione con un doppio pedice per la VDSdarà origine a una tensione negativa per VDS, come mostrato sulle caratteristiche di Fig. 5.12. Qui puoi trovare IDSSa 6 mA, mentre una tensione di pinch-off a VGS= + 6V.

Per favore non lasciarti perplesso a causa della presenza del tuo segno meno per la VDS. Indica semplicemente che la sorgente ha un potenziale maggiore rispetto allo scarico.

Puoi vedere che le curve per alta VDSi livelli salgono improvvisamente a valori che sembrano illimitati. L'aumento indicato che è verticale simboleggia una situazione di guasto, il che significa che la corrente attraverso il dispositivo di canale è interamente controllata dalla circuiteria esterna in questo momento.

Sebbene questo non sia evidente nella Fig. 5.10 per il dispositivo a canale n, potrebbe essere una possibilità con una tensione sufficientemente alta.

Questa regione può essere eliminata se la VDS (max)è annotato dalla scheda tecnica del dispositivo e il dispositivo è configurato in modo tale che l'effettiva VDSvalore è inferiore a questo valore annotato per qualsiasi VGS.

Precedente: 5 migliori circuiti amplificatori da 40 Watt esplorati Successivo: 2N3055 Datasheet, Pinout, Application Circuits