Uno stadio tampone fondamentalmente uno stadio intermedio rinforzato che consente alla corrente di ingresso di raggiungere l'uscita senza essere influenzata dal carico in uscita.

In questo post cercheremo di capire cosa sono i buffer digitali, e daremo uno sguardo alla sua definizione, simbolo, tabella di verità, doppia inversione usando la logica 'NOT' gate, digital buffer fan out fan in, tri-state buffer, Buffer a tre stati equivalente, buffer a tre stati attivo 'HIGH', buffer a tre stati invertente 'HIGH', buffer a tre stati attivo 'LOW', buffer a tre stati invertito attivo 'LOW', controllo del buffer a tre stati , controllo del bus dati del buffer a tre stati e infine faremo una panoramica sui circuiti integrati del buffer digitale e del buffer a tre stati comunemente disponibili.

In uno dei post precedenti abbiamo appreso della porta logica 'NOT' che viene anche chiamata inverter digitale. In una porta NOT l'uscita è sempre complementare all'ingresso.

Quindi, se l'ingresso è “ALTO” l'uscita diventa “BASSA”, se l'ingresso è “BASSO” l'uscita diventa “ALTA”, quindi questo è chiamato inverter.

Potrebbe esserci una situazione in cui l'uscita deve essere separata o isolata dall'ingresso, o nei casi in cui l'ingresso può essere piuttosto debole e deve pilotare carichi che richiedono una corrente più elevata senza invertire la polarità del segnale utilizzando un relè, o un transistor ecc. In tali situazioni i buffer digitali diventano utili e vengono applicati efficacemente come buffer tra la sorgente del segnale e l'effettivo stadio di pilotaggio del carico.

Come porte logiche che può fornire l'uscita del segnale come l'ingresso e agire come stadio buffer intermedio è chiamato buffer digitale.

Un buffer digitale non esegue alcuna inversione del segnale alimentato e non è nemmeno un dispositivo 'decisionale', come il gate logico 'NOT', ma fornisce la stessa uscita dell'ingresso.

Illustrazione del buffer digitale:

Il simbolo sopra è simile alla porta logica 'NOT' senza la 'o' sulla punta del triangolo, il che significa che non esegue alcuna inversione.

L'equazione booleana per il buffer digitale è Y = A.

'Y' è l'ingresso e 'A' l'uscita.

Tabella della verità:

Doppia inversione tramite porte logiche 'NOT':

Un buffer digitale può essere costruito utilizzando due porte logiche 'NOT' nel modo seguente:

Il segnale di ingresso viene prima invertito dalla prima porta NOT sul lato sinistro e il segnale invertito viene quindi ulteriormente invertito dalla successiva porta 'NOT' sul lato destro, che rende l'uscita uguale all'ingresso.

Perché vengono utilizzati i buffer digitali

Ora potresti grattarti la testa perché esiste anche il buffer digitale, non fa alcuna operazione come le altre porte logiche, potremmo semplicemente buttare il buffer digitale fuori da un circuito e collegare un pezzo di cavo …… .corretto? Beh, non proprio.

Ecco la risposta : Una porta logica non richiede una corrente elevata per eseguire alcuna operazione. Richiede solo un livello di tensione (5V o 0V) a bassa corrente è sufficiente.

Tutti i tipi di porte logiche supportano principalmente un amplificatore integrato in modo che l'uscita non dipenda dai segnali di ingresso. Se mettiamo in cascata due porte logiche 'NOT' in serie, otteniamo la stessa polarità del segnale dell'ingresso sul pin di uscita ma, con una corrente relativamente più alta. In altre parole, il buffer digitale funziona come un amplificatore digitale.

Un buffer digitale può essere utilizzato come stadio di isolamento tra gli stadi del generatore di segnale e gli stadi del driver, inoltre aiuta a prevenire l'impedenza che influisce su un circuito da un altro.

Un buffer digitale può fornire una maggiore capacità di corrente che può essere utilizzata per pilotare i transistor di commutazione in modo più efficiente.

Il buffer digitale fornisce un'amplificazione maggiore, chiamata anche capacità di 'fan-out'.

Capacità di fan-out del buffer digitale:

FAN-OUT : Il fan-out può essere definito come il numero di porte logiche o circuiti integrati digitali che possono essere pilotati in parallelo da un buffer digitale (o da qualsiasi circuito integrato digitale).

Un tipico buffer digitale ha un fan-out di 10, il che significa che il buffer digitale può pilotare 10 circuiti integrati digitali in parallelo.

FAN-IN : Il fan-in è il numero di ingressi digitali che possono essere accettati dalla porta logica digitale o dall'IC digitale.

Nello schema sopra, il buffer digitale ha fan-in 1, che significa un ingresso. Un gate logico 'AND' a '2 ingressi' ha due fan-in e così via.

Dallo schema di cui sopra è collegato un buffer ai 3 ingressi di tre differenti porte logiche.

Se colleghiamo solo un pezzo di filo al posto del buffer nel circuito sopra, il segnale di ingresso potrebbe non essere con una corrente sufficiente e causare una caduta di tensione attraverso le porte e potrebbe anche non riconoscere il segnale.

Quindi, in conclusione, un buffer digitale viene utilizzato per amplificare un segnale digitale con una corrente di uscita maggiore.

Buffer a tre stati

Ora sappiamo cosa fa un buffer digitale e perché esiste nei circuiti elettronici. Questi buffer hanno due stati 'HIGH' e 'LOW'. C'è un altro tipo di buffer chiamato 'Tri-state buffer'.

Questo buffer ha un pin aggiuntivo chiamato 'Enable pin'. Utilizzando il pin di abilitazione possiamo collegare o disconnettere elettronicamente l'uscita dall'ingresso.

Come un normale buffer, funziona come amplificatore digitale e fornisce il segnale di uscita uguale al segnale di ingresso, l'unica differenza è che l'uscita può essere collegata e scollegata elettronicamente dal pin di abilitazione.

Quindi viene introdotto un terzo stato, in questo l'uscita non è né “HIGH” né “LOW” ma uno stato di circuito aperto o alta impedenza all'uscita e non risponderà ai segnali di ingresso. Questo stato viene indicato come 'HIGH-Z' o 'HI-Z'.

Quanto sopra è il circuito equivalente del buffer a tre stati. Il pin di abilitazione può connettere o disconnettere l'uscita dall'ingresso.

Esistono quattro tipi di buffer a tre stati:

• Buffer a tre stati attivo “HIGH”

• Buffer a tre stati attivo “LOW”

• Buffer attivo a tre stati invertente 'HIGH'

• Buffer attivo a tre stati invertente 'LOW'

Diamo un'occhiata a ciascuno di essi in sequenza.

Buffer a tre stati attivo 'HIGH'

Nel buffer a tre stati attivo 'HIGH' (ad esempio: 74LS241) il pin di uscita viene collegato al pin di ingresso quando applichiamo 'HIGH' o '1' o un segnale positivo al pin di abilitazione.

Se applichiamo 'LOW' o '0' o un segnale negativo al pin di abilitazione, l'uscita viene scollegata dall'ingresso e passa allo stato 'HI-Z' dove l'uscita non risponderà all'ingresso e l'uscita sarà in stato di circuito aperto.

Buffer a tre stati attivo “LOW”

Qui l'uscita sarà collegata all'ingresso quando applichiamo “LOW” o “0” o un segnale negativo al pin di abilitazione.

Se applichiamo 'HIGH' o '1' o un segnale positivo per abilitare il pin, l'uscita viene scollegata dall'ingresso e l'uscita sarà nello stato 'HI-Z' / stato di circuito aperto.

Tabella della verità:

Buffer a tre stati invertente 'HIGH' attivo

Nel buffer Tri-state invertente “HIGH” attivo (esempio: 74LS240), il gate funge da gate logico “NOT” ma, con il pin di abilitazione.

Se applichiamo “HIGH” o “1” o segnale positivo all'ingresso di abilitazione il cancello si attiva e si comporta come una normale porta logica “NOT” dove la sua uscita è inversione / complementare dell'ingresso.

Se applichiamo 'LOW' o '0' o un segnale negativo al pin di abilitazione, l'uscita sarà in 'HI-Z' o in stato di circuito aperto.

Tabella della verità:

Buffer a tre stati invertente attivo 'LOW':

Nel buffer a tre stati invertente 'LOW' attivo, il gate funge da gate 'NOT' logico ma con il pin di abilitazione.

Se applichiamo “LOW” o “0” o un segnale negativo per abilitare il pin, il gate si attiva e funziona come un normale gate logico “NOT”.

Se applichiamo 'HIGH' o '1' o un segnale positivo per abilitare il pin, il pin di uscita sarà nello stato 'HI-Z' / stato di circuito aperto.

Tabella della verità:

Controllo del buffer a tre stati:

Da quanto sopra abbiamo visto che un buffer può fornire l'amplificazione digitale e che i buffer a tre stati possono scollegare completamente la sua uscita dall'ingresso e fornire uno stato di circuito aperto.

In questa sezione apprenderemo l'applicazione del buffer a tre stati e come viene utilizzato nei circuiti digitali per la gestione efficiente della comunicazione dei dati.

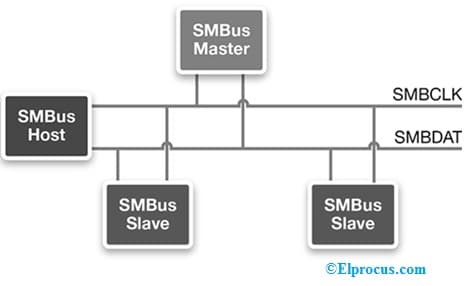

Nei circuiti digitali possiamo trovare un bus dati / fili che trasportano dati, trasportano tutti i tipi di dati in un unico bus per ridurre la congestione del cablaggio / ridurre le tracce di PCB e anche ridurre i costi di produzione.

A ciascuna estremità del bus sono collegati più dispositivi logici, microprocessori e microcontrollori che cercano di comunicare tra loro simultaneamente, creando qualcosa chiamato contesa.

La contesa si verifica in un circuito quando alcuni dispositivi in un bus pilotano 'HIGH' e alcuni dispositivi guidano 'LOW' simultaneamente, il che causa un cortocircuito e danni in un circuito.

Il buffer a tre stati può evitare tali contese e inviare e ricevere correttamente i dati su un bus.

Il buffer a tre stati viene utilizzato per isolare dispositivi logici, microprocessori e microcontrollori l'uno dall'altro in un bus dati. Un decodificatore consente a un solo set di buffer a tre stati di passare i dati attraverso il bus.

Diciamo che se il set di dati 'A' è collegato a un microcontrollore, il set di dati 'B' a un microprocessore e il set di dati 'C' ad alcuni circuiti logici.

Nello schema sopra, tutti i buffer sono buffer attivi a tre stati alti.

Quando il decoder imposta l'ENA “ALTO” il set di dati “A” è abilitato, ora il microcontrollore può inviare i dati attraverso il bus.

Il resto dei due set di dati 'B' e 'C' sono in 'HI-Z' o stato di impedenza molto alta che isola elettricamente il microprocessore ei circuiti logici dal bus, che è attualmente utilizzato dal microcontrollore.

Quando il decodificatore imposta ENB 'ALTO', il set di dati 'B' può inviare dati sul bus e il resto dei set di dati 'A' e 'C' sono isolati dal bus nello stato 'HI-Z'. Allo stesso modo, per quando il set di dati 'C' è abilitato.

Il bus di dati viene utilizzato da uno qualsiasi dei set di dati 'A' o 'B' o 'C' in un determinato momento per evitare conflitti.

Possiamo anche stabilire una comunicazione duplex (bidirezionale) collegando due buffer a tre stati in parallelo e in direzione opposta. I pin di abilitazione possono essere utilizzati come controllo della direzione. Per questo tipo di applicazioni può essere utilizzato IC 74245.

Ecco l'elenco comunemente disponibile di buffer digitali e buffer a tre stati:

• Buffer non invertente esadecimale 74LS07

• 74LS17 Hex Buffer / Driver

• Buffer ottale / driver di linea 74LS244

• Buffer bidirezionale ottale 74LS245

• Tampone non invertente esadecimale CD4050

• Buffer esadecimale a tre stati CD4503

• HEF40244 tampone ottale a tre stati

Questo conclude la nostra discussione su come funzionano i buffer digitali e le loro varie configurazioni digitali, spero che ti abbia aiutato a capire bene i dettagli. Se hai ulteriori domande o suggerimenti, esprimi le tue domande nella sezione commenti, potresti ottenere una risposta rapida.

Precedente: Come funzionano le porte logiche Avanti: Comprensione dei resistori pull-up e pull-down con diagrammi e formule