Il processore MicroBlaze è stato sviluppato nel 2002 per integrare diverse funzionalità complicate per soddisfare la nuova e crescente domanda del mercato. Pertanto, il processore MicroBlaze è un elemento essenziale all'interno del portafoglio di fascia bassa di Xilinx per consentire uno sviluppo più rapido del sistema che contiene Artix®-7 FPGA , SoC Spartan®-6, Zynq®-7000 AP. Questo processore è estremamente configurabile, quindi può essere utilizzato come processore integrato o microcontrollore all'interno di FPGA e utilizzato anche come coprocessore nei SoC Zynq-7000 AP basati su ARM Cortex-A9. Questo articolo fornisce brevi informazioni su Processore MicroBlaze – architettura e lavoro con le applicazioni.

Cos'è il processore Microblaze?

Il microprocessore software progettato principalmente per gli FPGA di Xilinx è noto come processore MicroBlaze. Questo processore è semplicemente implementato all'interno del tessuto logico e di memoria per uso generale degli FPGA di Xilinx. Questo processore è simile all'architettura DLX basata su RISC e dispone di un sistema di interconnessione flessibile in modo da supportare diverse applicazioni embedded. Il bus I/O principale e l'interconnessione AXI di MicroBlaze è un bus di transazione mappato in memoria con una funzione master-slave.

MicroBlaze utilizza un bus LMB dedicato per accedere alla memoria locale e fornisce una rapida memorizzazione su chip. Molte parti di questo processore possono essere configurate dall'utente come la dimensione della cache, la profondità dell'unità di gestione della memoria della pipeline, le periferiche integrate e le interfacce bus.

Caratteristiche di Microblaze

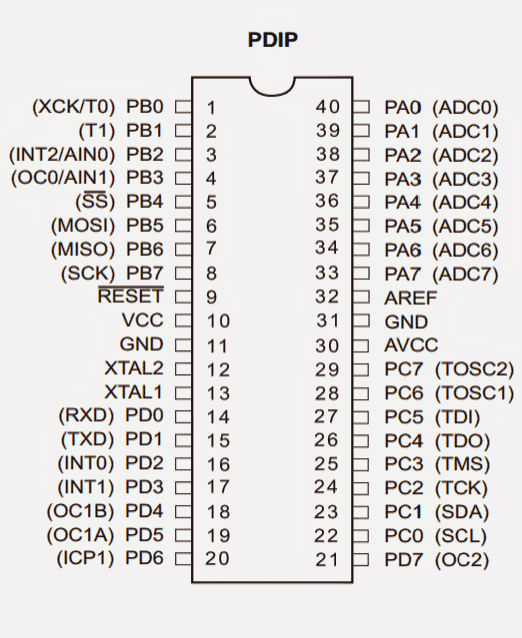

Il caratteristiche di Microblaz e includere quanto segue. Dispone di 32 registri di uso generale.

- Dispone di parole di istruzione a 32 bit, incluse 2 modalità di indirizzamento e 3 operandi.

- Il bus di indirizzi è a 32 bit.

- Ha una pipeline a 3 stadi o una pipeline a 5 stadi.

- Un'unità di blocco ALU con un cambio.

- L'architettura di Harvard include dati a 32 bit e bus di indirizzi.

- Interfaccia dati e istruzioni LMB o bus di memoria locale.

- Interfacce di flusso AX14 e AX14.

- Unità a virgola mobile e unità di gestione della memoria.

- Supporta lockstep.

- Interfaccia di debug e traccia.

Architettura Microbaze

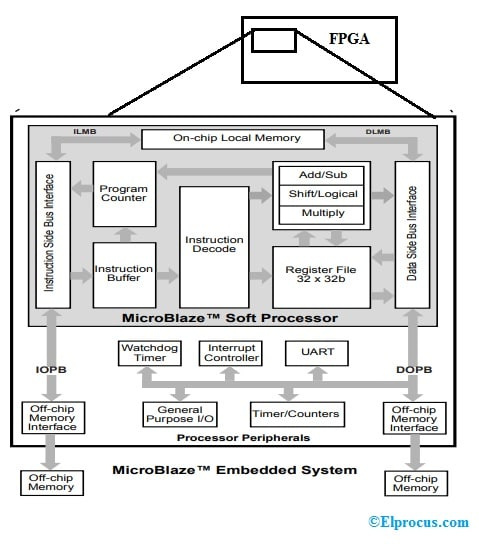

Lo schema a blocchi del processore MicroBlaze è mostrato di seguito. Questo processore MicroBlaze è estremamente personalizzabile e supporta oltre 70 opzioni di design. Questa architettura mostra caratteristiche hardware permanenti e opzioni configurabili come la cache delle istruzioni o dei dati, l'unità di gestione della memoria, l'unità a virgola mobile, ecc.

Un sistema incorporato assemblato attorno a un processore MicroBlaze include principalmente MicroBlaze Soft Processor Core, memoria locale su chip, interconnessioni bus standard e periferiche OPB (bus periferico su chip). Un sistema di processori MicroBlaze varia principalmente da un core del processore da una memoria locale a un sistema di grandi dimensioni che include diversi MicroBlaze processori , memoria esterna e molte periferiche OPB.

Nucleo morbido del processore

Il soft core del processore di MicroBlaze è fondamentale per il sistema embedded MicroBlaze. Questo è un processore RISC a 32 bit molto veloce ed efficiente che ha le seguenti caratteristiche.

- Il set di istruzioni è ortogonale.

- Bus dati e istruzioni separati.

- Registri per uso generico a 32 bit.

- Ha un cambio a barilotto completo a 32 bit opzionale.

- Interfacce integrate per OCM veloce o memoria su chip e OPB (On-chip Peripheral Bus) standard di settore di IBM.

Le implementazioni all'interno di Virtex-II e dispositivi successivi supportano la moltiplicazione dell'hardware.

Memoria locale su chip

La memoria sincrona è una memoria locale utilizzata principalmente per consentire la RAM a blocchi su chip.

Interconnessioni bus standard

Le interfacce bus sul lato istruzioni e dati includono un'interfaccia per la memoria locale chiamata LMB (Local Memory Bus) e un'interfaccia per il bus periferico su chip di IBM. Quindi possiamo progettare sistemi che si attengono rigorosamente all'architettura di Harvard, altrimenti, per condividere le risorse, possiamo utilizzare un singolo OPB in combinazione tramite un arbitro del bus.

Il bus di memoria locale offre un ingresso a ciclo singolo assicurato per la RAM a blocchi su chip. Questo è un protocollo bus molto efficiente, semplice e a master singolo ed è perfetto per interfacciare la memoria locale veloce. L'OPB o On-chip Peripheral Bus è un bus multimaster a 32 bit, perfetto per unire periferiche e memoria esterna al core del processore MicroBlaze.

Periferiche bus periferiche su chip

Il sistema hardware MicroBlaze è completato da periferiche OPB per fornire diverse funzioni come Watchdog Timer o Timebase, Timer o contatori per uso generico, IC (Interrupt Controller), diversi controller come SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, I/O per uso generico, UART 16450/550 ed Ethernet 10/100 MAC. Inoltre, possiamo anche aggiungere e definire periferiche principalmente per funzioni personalizzate, altrimenti un'interfaccia per un design che esiste nell'FPGA.

Set di istruzioni per Microblaze

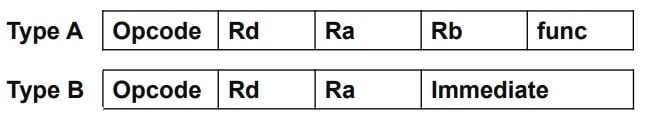

I set di istruzioni Microblaze sono aritmetica, logica, branch, load/store e altri. La dimensione di tutte le istruzioni è fissa. Come operandi possono essere dati al massimo 3 registri. Microblaze include due formati di istruzioni Tipo A e Tipo B che sono mostrati di seguito.

Il formato di istruzione di tipo A viene utilizzato principalmente per le istruzioni registro-registro. Quindi include il codice operativo, una singola destinazione e due registri di origine. Il formato di istruzione di tipo B viene utilizzato principalmente per le istruzioni immediate di registro che includono il codice operativo, la destinazione singola e i registri di origine singola e una sorgente di valore immediato a 16 bit.

Nei due formati di istruzione precedenti, l'opcode è un codice operativo, Rd è un registro di destinazione codificato con 5 bit, Ra e Rb sono registri sorgente in cui ciascuno codificato con 5 bit e Immediate è un valore a 16 bit.

Istruzioni aritmetiche

Di seguito vengono fornite le istruzioni aritmetiche di tipo A e di tipo B.

Digitare un

|

AGGIUNGERE Rd, Ra, Rb Inserisci |

Rd = Ra+Rb, Carry flag influenzato |

|

AGGIUNGERE K Rd, Ra, Rb Aggiungi e mantieni il trasporto |

Rd = Ra+Rb, Carry flag non ha effetto |

| RSUB Rd, Ra, Rb Sottrazione inversa |

Rd = R-Rb, Carry flag non influenzato |

Tipo B

|

AGGIUNGI I Rd, Ra, Imm aggiungi immediato |

Rd = Ra+segnoEstendi32 (Imm) |

|

AGGIUNGI IK Rd, Ra, Imm aggiungi immediatamente e mantieni il trasporto |

Rd = Ra+ segnoExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm sottrazione inversa con immediato |

Rd = Ra+ segnoExtend32 (Imm) -Ra |

| SRA Rd, Ra spostamento aritmetico a destra |

Rd = (Ra>>1) |

Istruzioni logiche

Di seguito sono riportate le istruzioni logiche di tipo A e di tipo B.

Digitare un

|

OPPURE Rd, Ra, Rb Logico o |

Rd = Ra| Rb |

|

E Rd, Ra, Rb Aggiunta logica |

Rd = Ra e Rb |

| XOR Rd, Ra, Rb Xor logico |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logico e non |

Rd = Ra & (Rb) |

Tipo B

|

ORI Rd, Ra, Imm logico OR con immediato |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm logico AND con immediato |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logo XOR con immediato |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logico E NON con immediato |

Rd = Ra & (signExtend32 (Imm)) |

Istruzioni per le filiali - Incondizionate

Modificare il registro del contatore del programma

| SPOSA Imm diramazione immediata con ritardo immediato |

PC = PC+ signExtend32 (Imm) consentire l'esecuzione dello slot di ritardo |

| BRLID Rd, Imm diramazione e collegamento immediato con ritardo immediato (richiamo di funzione) |

Rd = PC PC = PC+& signExtend32 (Imm) consentire l'esecuzione dello slot di ritardo |

| RTSD Ra, Imm ritorno dal sottoprogramma |

PC = Ra + segno Estendi32 (Imm) consentire l'esecuzione dello slot di ritardo |

| RTID Ra, Imm ritorno dall'interruzione |

PC = Ra + segno Estendi32 (Imm) consentire l'esecuzione dello slot di ritardo impostare l'abilitazione dell'interruzione in MSR |

Istruzioni per la filiale - Incondizionato1

Modificare il registro del contatore del programma quando una condizione è soddisfatta

| BEQI Ra, Imm ramo se uguale |

PC = PC+ signExtend32 (Imm) Se Ra = = 0 |

| MASH Ra, Imm ramo se non uguale |

Rd = PC PC = PC+& signExtend32 (Imm) Se Ra! = 0 |

Branch Istruzioni- Incondizionato2

Modificare il registro del contatore del programma quando una condizione è soddisfatta

| BLTI Ra, Imm ramo se inferiore a |

PC = PC+ signExtend32 (Imm) Se Ra < 0 |

| BLEI Ra, Imm ramo se minore uguale a |

Rd = PC PC = PC+& signExtend32 (Imm) Se Ra!< = 0 |

| BGTI Ra, Imm ramo se maggiore di |

PC = PC+ signExtend32 (Imm) Se Ra!> 0 |

| BGEI Ra, Imm ramo se maggiore uguale a |

PC = PC+segnoEstendi32 (Imm) Se Ra!>= 0 |

Istruzioni di caricamento/memorizzazione -Tipo A

| LW Rd, Ra, Rb Carica parola |

Indirizzo = Ra+Rb Rd = *Indirizzo |

| SW Rd, Ra, Rb Memorizza parola |

Indirizzo – Ra+Rb *Indirizzo = Rd |

Tipo B

| LWI Rd, Ra, Imn Carica parola immediata |

Indirizzo = Ra + segnoExtend32 (Imm) Rd = *Indirizzo |

| SW Rd, Ra, Imm Memorizza parola immediata |

Indirizzo = Ra + segnoExtend32 (Imm) *Indirizzo = Rd |

Altre istruzioni

| IMM, Imm immediato |

Estendere l'Imm di un'istruzione di tipo B precedente a 32 bit. |

| MFS Rd, Sa Passaggio dal registro per scopi speciali |

Rd = Sa Sa- registro per scopi speciali, operando sorgente

|

| MTS Sd, Ra Passa al registro per scopi speciali |

Sd = Ra Sd - registro per scopi speciali, operando di destinazione |

Registri

L'architettura del processore MicroBlaze è completamente ortogonale e include registri per scopi generici a 32 bit e registri per scopi speciali a 32 bit come Program Counter e Machine Status Register.

Architettura della conduttura

MicroBlaze utilizza un'architettura di pipeline a 3 fasi che include fasi di recupero, decodifica e complete. Automaticamente, l'inoltro dei dati, i rami e lo stallo della pipeline vengono determinati all'interno dell'hardware.

Carica o archivia l'architettura

MicroBlaze supporta la memoria in tre dimensioni di dati: 8 bit (Byte), 16 bit (Halfword) e 32 bit (Word). Quindi, gli accessi alla memoria sono sempre allineati alle dimensioni dei dati. Questo è un processore Big Endian che utilizza l'indirizzo dell'indirizzo Big Endian e le convenzioni di etichettatura una volta che si accede alla memoria.

Interruzioni

Una volta che si verifica un'interruzione, questo processore interromperà l'esecuzione in corso per gestire la richiesta di interruzione tramite il branching per interrompere l'indirizzo del vettore e memorizzare l'indirizzo dell'istruzione che deve essere eseguito. Questo processore interromperà gli interrupt futuri cancellando il flag IE (Interrupt Enable) all'interno dell'MSR (Machine Status Register).

Come funziona Microblaze?

Il processore MicroBlaze supporta una larghezza del bus a 32 bit e questo core del processore è un motore basato su RISC che include un file di registro basato su RAM LUT a 32 bit tramite istruzioni separate per l'accesso alla memoria e ai dati.

Questo processore supporta semplicemente sia la BlockRAM su chip che la memoria esterna. Simile all'IBM PowerPC; tutte le periferiche utilizzano il bus CoreConnect OPB simile, quindi; le periferiche del processore sono ben abbinate con PowerPC su Virtex-II Pro.

Il processore MicroBlaze offre una flessibilità completa per scegliere la combinazione di memoria, periferiche e funzionalità di interfaccia che ti forniranno il sistema preciso di cui hai bisogno su un singolo FPGA con un costo inferiore.

Differenza B/N Microblaze Vs Risc-V

Il differenza tra MicroBlaze e RISC v include il seguente.

|

Microfiamma |

Risc-V |

| È un core di microprocessore morbido progettato principalmente per Xilinx FPGA.

|

RISC-V è un'architettura di set di istruzioni radicata nei principi RISC.

|

| Utilizza l'architettura RISC di Harvard. | Utilizza l'architettura del set di istruzioni. |

| La sua licenza è proprietaria (Xilinx) | La sua licenza è open source. |

| La profondità della condotta è 3 o 5. | La profondità della condotta è 5. |

| La sua prestazione è di 280 DMIP. | La sua prestazione è di 250 DMIP. |

| La sua velocità è di 235 MHz. | La sua velocità è di 250 MHz. |

| Ha 1027 LUT. | Ha 4125 LUT. |

| L'implementazione della tecnologia utilizzata è Xilinx FPGA. | L'implementazione della tecnologia utilizzata è FPGA/ASIC. |

Vantaggi di Microblaze

Il vantaggi di MicroBlaze include il seguente.

- È economico.

- È altamente configurabile.

- Le sue prestazioni sono elevate rispetto a ARM.

- È supportato da un kit di sviluppo integrato.

- È un morbido microprocessore nucleo.

- Per aiutarti a organizzare rapidamente la tua applicazione, questo processore include tre configurazioni fisse correlate a note classi di processori microcontrollore, tempo reale e processore applicativo.

Applicazioni Microblaze

Il applicazioni di MicroBlaze include il seguente.

- Questo processore soddisfa molti diversi requisiti applicativi come industriale, automobilistico, medico e di consumo, ecc.

- Le applicazioni di MicroBlaze vanno da semplici macchine a stati basate su software a controller complessi utilizzati in applicazioni embedded o dispositivi basati su Internet.

- È ottimizzato per applicazioni embedded come controllo industriale, automazione d'ufficio e automotive.

- MicroBlaze è in grado di comunicare con un ampio set di periferiche per adattarsi ad applicazioni di media scala.

- La natura morbida di questo processore lo rende personalizzabile per diverse applicazioni in cui i progettisti possono scambiare caratteristiche per dimensioni per soddisfare obiettivi di prezzo e prestazioni per applicazioni mediche, automobilistiche, industriali e di sicurezza.

Quindi, questo è tutto una panoramica del Microblaze processore. Si tratta di un core soft processor RISC programmabile a 32 bit con funzionalità complete. Questo processore soddisfa diversi requisiti all'interno di diversi settori come i mercati consumer, medicale, industriale, automobilistico e delle infrastrutture di comunicazione. È estremamente configurabile, quindi utilizzato come processore integrato o microcontrollore all'interno di FPGA altrimenti come coprocessore per ARM. Ecco una domanda per te, cos'è l'FPGA?